Rev. 1.0, 02/00, page 928 of 1141

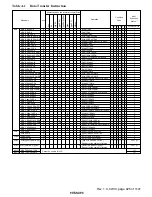

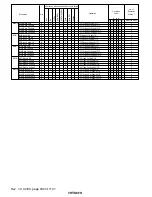

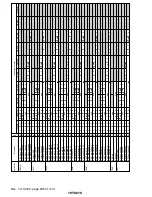

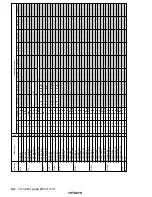

Table A.4

Shift Instructions

SHAL.B Rd

SHAL.B #2,Rd

SHAL.W Rd

SHAL.W #2,Rd

SHAL.L ERd

SHAL.L #2,ERd

SHAR.B Rd

SHAR.B #2,Rd

SHAR.W Rd

SHAR.W #2,Rd

SHAR.L ERd

SHAR.L #2,ERd

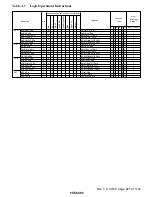

SHLL.B Rd

SHLL.B #2,Rd

SHLL.W Rd

SHLL.W #2,Rd

SHLL.L ERd

SHLL.L #2,ERd

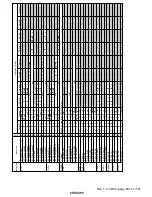

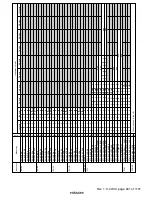

SHLR.B Rd

SHLR.B #2,Rd

SHLR.W Rd

SHLR.W #2,Rd

SHLR.L ERd

SHLR.L #2,ERd

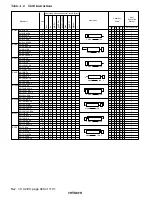

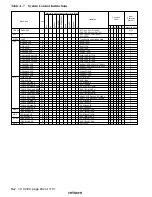

ROTXL.B Rd

ROTXL.B #2,Rd

ROTXL.W Rd

ROTXL.W #2,Rd

ROTXL.L ERd

ROTXL.L #2,ERd

ROTXR.B Rd

ROTXR.B #2,Rd

ROTXR.W Rd

ROTXR.W #2,Rd

ROTXR.L ERd

ROTXR.L #2,ERd

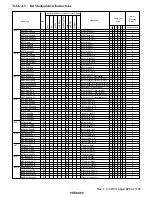

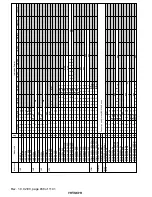

ROTL.B Rd

ROTL.B #2,Rd

ROTL.W Rd

ROTL.W #2,Rd

ROTL.L ERd

ROTL.L #2,ERd

ROTR.B Rd

ROTR.B #2,Rd

ROTR.W Rd

ROTR.W #2,Rd

ROTR.L ERd

ROTR.L #2,ERd

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

B

B

W

W

L

L

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

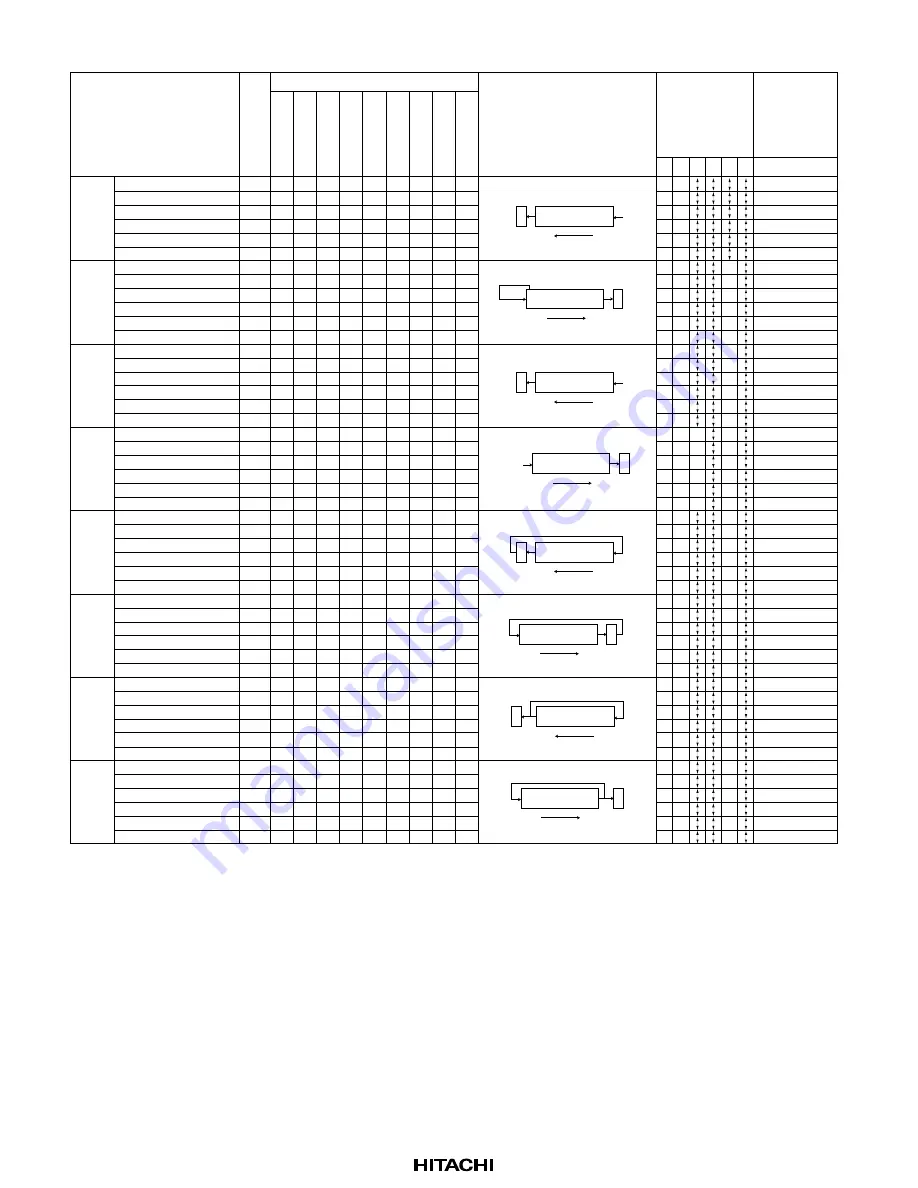

SHAL

SHAR

SHLL

SHLR

ROTXL

ROTXR

ROTL

ROTR

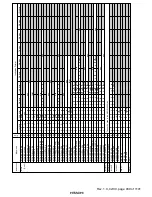

Mnemonic

Size

#xx

Rn

@ERn

@(d,ERn)

@-ERn/@ERn+

@aa

@(d,PC)

@@aa

—

Operation

Condition

Code

I

H N Z V C

Advanced Mode

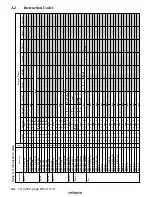

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

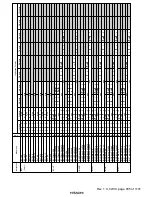

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

0

0

0

0

0

C

0

MSB

LSB

C MSB

LSB

C MSB

LSB

C

MSB

LSB

C

MSB

LSB

C

0

MSB

LSB

C

0

MSB

LSB

C

MSB

LSB

Addressing Mode and Instruction Length (Bytes)

No of

Execution

States

*1