Rev. 1.0, 02/00, page xiv of 19

26.3.2

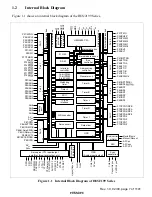

Block Diagram.................................................................................................. 566

26.3.3

Register Configuration...................................................................................... 568

26.3.4

Register Description ......................................................................................... 569

26.3.5

Operation .......................................................................................................... 574

26.4

HSW (Head-switch) Timing Generator ............................................................................ 589

26.4.1

Overview .......................................................................................................... 589

26.4.2

Block Diagram.................................................................................................. 589

26.4.3

HSW Timing Generator Configuration ............................................................ 591

26.4.4

Register Configuration...................................................................................... 592

26.4.5

Register Description ......................................................................................... 592

26.4.6

Operation .......................................................................................................... 606

26.4.7

Interrupts........................................................................................................... 612

26.4.8

Cautions ............................................................................................................ 613

26.5

High-Speed Switching Circuit for Four-Head Special Playback ...................................... 614

26.5.1

Overview .......................................................................................................... 614

26.5.2

Block Diagram.................................................................................................. 614

26.5.3

Pin Configuration ............................................................................................. 615

26.5.4

Register Description ......................................................................................... 615

26.6

Drum Speed Error Detector .............................................................................................. 618

26.6.1

Overview .......................................................................................................... 618

26.6.2

Block Diagram.................................................................................................. 618

26.6.3

Register Configuration...................................................................................... 620

26.6.4

Register Description ......................................................................................... 621

26.6.5

Operation .......................................................................................................... 626

26.6.6

f

H

Correction in Trick Play Mode ..................................................................... 628

26.7

Drum Phase Error Detector............................................................................................... 629

26.7.1

Overview .......................................................................................................... 629

26.7.2

Block Diagram.................................................................................................. 630

26.7.3

Register Configuration...................................................................................... 631

26.7.4

Register Description ......................................................................................... 632

26.7.5

Operation .......................................................................................................... 635

26.7.6

Phase Comparison ............................................................................................ 637

26.8

Capstan Speed Error Detector........................................................................................... 638

26.8.1

Overview .......................................................................................................... 638

26.8.2

Block Diagram.................................................................................................. 639

26.8.3

Register Configuration...................................................................................... 640

26.8.4

Register Description ......................................................................................... 641

26.8.5

Operation .......................................................................................................... 646

26.9

Capstan Phase Error Detector ........................................................................................... 648

26.9.1

Overview .......................................................................................................... 648

26.9.2

Block Diagram.................................................................................................. 648

26.9.3

Register Configuration...................................................................................... 650

26.9.4

Register Description ......................................................................................... 651