Rev. 1.0, 02/00, page 333 of 1141

16.3

Operation

16.3.1

Operation of Timer X1

•

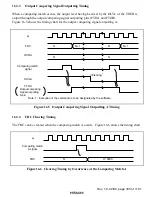

Output Comparing Operation

Right after resetting, the FRC is initialized to H'0000 to start counting up. The inputting clock

can be selected from among three different types of internal clocks or the external clock by

setting the CKS1 and CKS0 of the TCRX.

The contents of the FRC are always being compared with the OCRA and OCRB and, when

the value of these two match, the level set by the the OLVLA and OLVLB of the TOCR is

output through the FTOA pin and FTOB pin.

After resetting, 0 will be output through the FTOA and FTOB pins until the first compare

matching occurs.

Also, when the CCLRA of the TCSRX is being set to 1, the FRC will be cleared to H'0000

when the comparing match A occurs.

•

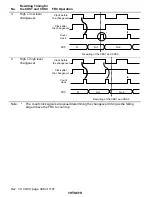

Input Capturing Operation

Right after resetting, the FRC is initialized to H'0000 to start counting up. The inputting clock

can be selected from among three different types of internal clocks or the external clock by

setting the CKS1 and CKS0 of the TCRX.

The inputs are transferred to the IEDGA through IEDGD of the TCRX through the FTIA

through FTID pins and, at the same time, the ICFA through ICFD of the TCSRX are set to 1.

At this time, if the ICIAE through ICIED of the TIER are being set to 1, due interrupt request

will be issued to the CPU.

When the BUFEA and BUFEB of the TCRX are set to 1, the ICRC and ICRD work as the

buffer register, respectively, of the ICRA and ICRB. When the edge selected by setting the

IEDGA through IEDGD of the TCRX is input through the FTIA and FTIB pins, the value at

the time of the FRC is transferred to the ICRA and ICRB and, at the same time, the values of

the ICRA and ICRB before updating are transferred to the ICRC and ICRD. At this time,

when the ICFA and ICFB are being set to 1 and if the ICIAE and ICIBE of the TIER are being

set to 1, due interrupt request will be issued to the CPU.