Rev. 1.0, 02/00, page 399 of 1141

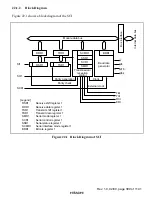

22.1.2

Block Diagram

Figure 22.1 shows a block diagram of the SCI.

SI1

SO1

SCK1

Clock

External clock

φ

φ

/4

φ

/16

φ

/64

TEI

TXI

RXI

ERI

RSR1

RDR1

TSR1

TDR1

SMR1

SCR1

SSR1

SCMR1

BRR1

: Receive shift register 1

: Receive data register 1

: Transmit shift register 1

: Transmit data register 1

: Serial mode register 1

: Serial control register 1

: Serial status register 1

: Serial interface mode register 1

: Bit rate register 1

SCMR1

SSR1

SCR1

SMR1

Transmission/

reception

control

Baud rate

generator

BRR1

Module data bus

Bus interface

Internal data bus

RDR1

TSR1

RSR1

Parity generation

Parity check

[Legend]

TDR1

Figure 22.1 Block Diagram of SCI