Rev. 1.0, 02/00, page 579 of 1141

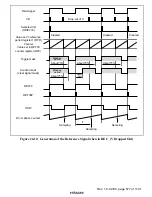

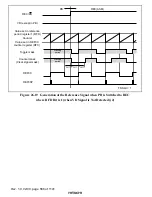

Cleared

Cleared

Reset

Value set in reference

period register 1 (RFD)

Counter

Value set in REF30

counter register (RFC)

External sync

signal

REF30

REF30P

Figure 26.12 Generation of REF30 Signal by the External Sync Signal

•

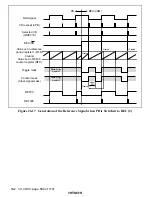

CREF Signal Generator

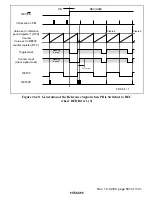

The CREF signal generator generates the CREF signal which is the reference signal to

control the phase of capstan.

To generate the CREF signal, set the 1/2 the reference period to the reference period

register 2 (CRF). If the set value matches the counter value, a toggle waveform is

generated corresponding to the 50 percent duty cycle, and a one-shot pulse is output at each

rising edge of the waveform. The counter of CREF signal generator is initialized to H'0000

and the phase of the toggle is cleared to L level when the mode shifts from PB (ASM) to

REC. The timing of clearing is selectable between immediately after the transition from

PB (ASM) to REC and the timing of DVCFG2 after the transition. Use bit 3 (CRD) of the

reference period mode register (RFM) for this selection.

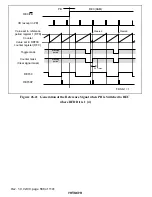

In the capstan phase error detection circuit, either REF30 signal or CREF signal can be

selected for the reference signal. Use either of them according to the use of the system.

Use the CREF signal to control the phase of the capstan at a period which is different from

the period used to control the phase of the drum. For the switching between REF30 and

CREF in the capstan phase control, see the description of capstan phase error detection

control register (CPGCR) in section 26.9.4, Register Description.