Rev. 1.0, 02/00, page 672 of 1141

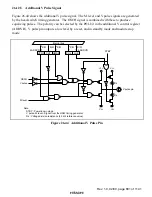

Digital Filter Control Register (DFUCR)

0

0

1

0

R/W

2

0

R/W

3

0

4

0

R/W

5

0

6

7

—

—

—

—

R/W

R/W

R/W

PTON

CP/DP

CFEPS

DFEPS

CFESS

DFESS

1

1

Bit :

Initial value :

R/W :

DFUCR is an 8-bit read/write register which controls the operation of the digital filter. Only a byte

access is valid. If a word access is attempted, correct operation is not guaranteed. It is initialized

to H'00 by a reset, or in stand-by or module stop mode.

Bits 7 and 6

Reserved: Cannot be modified and are always read as 1.

Bit 5

Phase System Computation Result PWM Output Bit (PTON): Outputs the computation

results of only the phase system to PWM. (The computation results of the drum phase system is

output to CAPPWM pin, and that of the capstan phase system is output to DRMPWM pin.)

Bit 5

PTON

Description

0

Outputs the results of ordinary computation of the filter to PWM pin

(Initial value)

1

Outputs the computation results of only the phase system to PWM pin

Bit 4

PWM Output Selection Bit (CP/

'3

'3

'3

'3

): Selects whether the phase system computation

results when PTON was set to 1 is output to the drum or capstan. The PWM of the selected side

outputs ordinary filter computation results (speed system of MIX).

Bit 4

CP/

'3

'3

'3

'3

Description

0

Outputs the drum phase system computation results (DRMPWM)

(Initial value)

1

Outputs the capstan phase system computation results (CAPPWM)