Rev. 1.0, 02/00, page 1108 of 1141

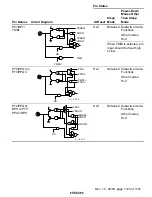

H'FFEA: Standby Control Register SBYCR: System Control

0

0

1

0

R/W

2

0

3

0

4

0

R/W

5

0

6

0

7

R/W

R/W

STS1

R/W

STS2

0

R/W

SSBY

STS0

SCK1

SCK0

Transition to sleep mode after execution of SLEEP instruction in

high-speed mode or medium-speed mode

Transition to subsleep mode after execution of SLEEP

instruction in subactive mode

Transition to stadby mode, subactive mode, or watch mode after

execution of SLEEP instruction in high-speed mode or medium-

speed mode

Transition to watch mode or high-speed mode after execution of

SLEEP instruction in subactive mode

0

1

Software standby

System clock select

System clock select

0

0

SCK0

SCK1

1

0

1

Bus master is in high-speed mode

Medium-speed clock is

φ

/16

Medium-speed clock is

φ

/32

1

Medium-speed clock is

φ

/64

0

0

STS1

STS2

1

Standby timer select bits

0

STS0

1

0

Standby time

8192 states

16384 states

32768 states

0

1

1

0

1

65536 states

1

*

Reserved

131072 states

262144 states

Note: *Don't care.

—

—

—

—

Bit

Initial value

R/W

:

:

: