Rev. 1.0, 02/00, page 612 of 1141

26.4.7

Interrupts

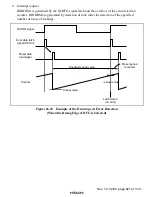

The HSW timing generator generates interrupts under the following conditions.

1

IRRHSW1 occurs when pattern data is written (OVWA, OVWB = 1) while FIFO is full

(FULL).

2

IRRHSW1 occurs when matching is detected while the STRIG bit of FIFO is 1.

3

IRRHSW1 occurs when the values of the 16-bit timer counter and 16-bit timing pattern

register match.

4

IRRHSW2 occurs when the 16-bit timer counter is cleared.

5

IRRHSW2 occurs when a VD signal (capture signal of the timer capture register) is received in

PB mode.

Condition 2 or 3, as well as 4 or 5, are selected by ISEL1 and ISEL2.