Rev. 1.0, 02/00, page 309 of 1141

15.5

Settings for Respective Functions

15.5.1

Mode Identification

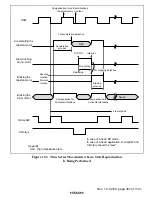

When making mode identification (2/4/6 identification) of the SP/LP/EP modes of reproducing

tapes, the TMRU-1 (CFG dividing circuit), TMRU-2 (capturing function/without reloading

function) and TMRU-3 (DVCTL dividing circuit) of the timer R should be used.

Timer R will be initialized to this mode identification status after a reset.

Under this status, the divided CFG should be written into the reloading register of the TMRU-1

and divided DVCTL should be written into the reloading register of the TMRU-3. When the

TMRU-3 underflows, the counter value of the TMRU-2 is captured. Such capturing register value

represents the number of the CFG within the DVCTL cycle.

Thus, timer R can work to count the number of the CFG corresponding to n times of DVCTL's or

to identify the mode being searched.

Settings

•

Setting the timer R mode register 1 (TMRM1)

CLR2 bit (bit 7) = 1: Works to clear after making the TMRU-2 capture.

RLD bit (bit 5) = 0: Sets the TMRU-3 without reloading function.

PS21 and PS20 (bits 3 and 2) = (0 and 0): The underflowing signals of the TMRU-1 are to

be used as the clock source for the TMRU-2.

RLD/CAP bit (bit 1) = 0: The TMRU-1 has been set to make the reload timer operation.

•

Setting the timer R mode register 2 (TMRM2)

LAT bit (bit 7) = 0: The underflowing signals of the TMRU-3 are to be used as the capture

signal for the TMRU-2.

PS11 and PS10 (bits 6 and 5) = (0 and 0): The leading edge of the CFG signal is to be used

as the clock source for the TMRU-1.

PS31 and PS30 (bits 4 and 3) = (0 and 0): The leading edge of the DVCTL signal is to be

used as the clock source for the TMRU-3.

CP/SLM bit (bit 2) = 0: The capture signal is to work to issue the TMRI3 interrupt request.

•

Setting the timer R load register 1 (TMRL1)

Set the dividing value for the CFG. The set value should become (n

−

1) when divided by

n.

•

Setting the timer R load register 3 (TMRL3)

Set the dividing value for the DVCTL. The set value should become (n

−

1) when divided

by n.