User Manual

56 of 562

V 1.0

2021-08-25

XDPP1100 technical reference manual

Digital power controller

Current sense (IS)

Lower-valued settings of

ispX_err_ratio_sel

are very sensitive and may cause false fault declaration,

particularly in noisy current sense environments. Therefore, it is recommended to use only the higher-valued

ispX_err_ratio_sel

settings of 6 or 7.

3.4

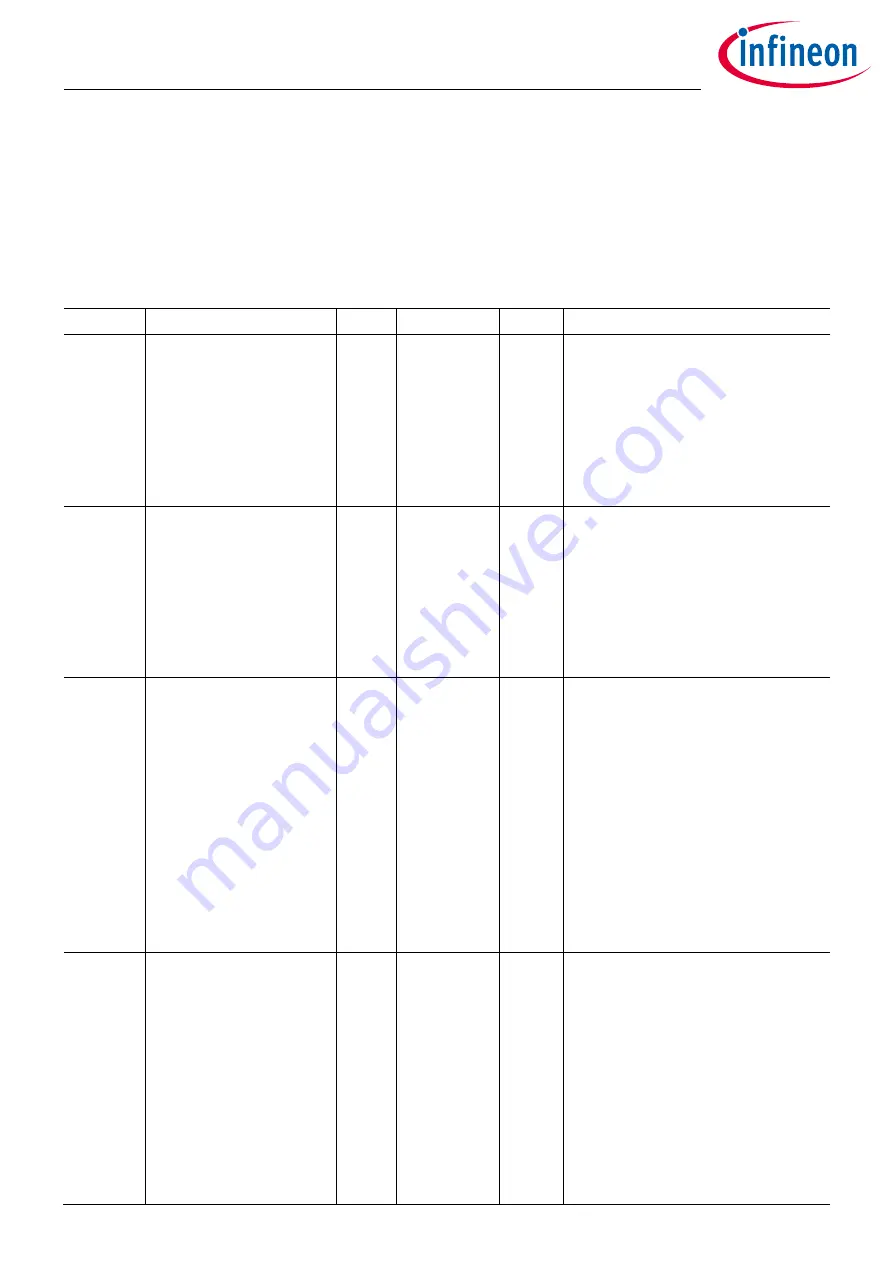

Current sense registers

The relevant current sense registers and their descriptions are provided in

Table 16

Current sense-related register descriptions

Peripheral Field name

Access Address

Bits

Description

analog

isen1_gain_mode

RW

7000_0400h [13:12] ISEN1 (ISEN) gain mode select.

Defines LSB weight of ISEN1 ADC.

Also defines expected reference

voltage level on IREF1 (IREF).

0: Reserved

1: LSB = 100 µV, IREF level = GND

2: LSB = 1.45 mV, IREF level = GND

3: LSB = 1.45 mV, IREF level = 1.2 V

analog

isen2_gain_mode

RW

7000_0400h [15:14] ISEN2 (BISEN) gain mode select.

Defines LSB weight of ISEN2 ADC.

Also defines expected reference

voltage level on IREF2 (BIREF).

0: Reserved

1: LSB = 100 µV, BIREF level = GND

2: LSB = 1.45 mV, BIREF level = GND

3: LSB = 1.45 mV, BIREF level = 1.2 V

isen

ce_ktrack_hiz

RW

7000_2400h

(ISEN)

7000_2800h

(BISEN)

[3:0]

Current sense tracking gain in the

HIZ state. The tracking gain defines

the relative strength of the IADC-

based correction term applied to

the emulated current waveform.

The HIZ state generally refers to the

state when all primary and

secondary switches are off. Note

that this register should be set to 0

for primary-side current sense and

for the boost topology.

LSB = 1/16 V/V, range = 0 to

15/16 V/V

isen

ce_ktrack_off

RW

7000_2400h

(ISEN)

7000_2800h

(BISEN)

[7:4]

Current sense tracking gain in the

off-state. The tracking gain defines

the relative stength of the IADC-

based correction term applied to

the emulated current waveform.

The off-state generally refers to the

state when the output inductor

current is in its downward slope

cycle (e.g., primary FETs off,

secondary FETs on in a bridge

topology). Note that this register

should be set to 0 for primary-side