User Manual

130 of 562

V 1.0

2021-08-25

XDPP1100 technical reference manual

Digital power controller

Digital pulse width modulator

The pulse width, t2

–

t1, for all modulation schemes is given in Equation (7.2):

𝑡

2

− 𝑡

1

= 𝐷 ∗ 𝑟𝑎𝑚𝑝_𝑚𝑎𝑥

(7.2)

D is the duty-cycle output of the compensation filter in the case of VMC. It should be noted that the pulse

generator is also capable of creating a pulse with LE at t2 and TE at t1. This pulse would have a pulse width

equal to (1

–

D) * ramp_max. The modulation scheme for both ramps is selected via register

rampX_m_flavor

(X = 0, 1) as shown in

Table 36

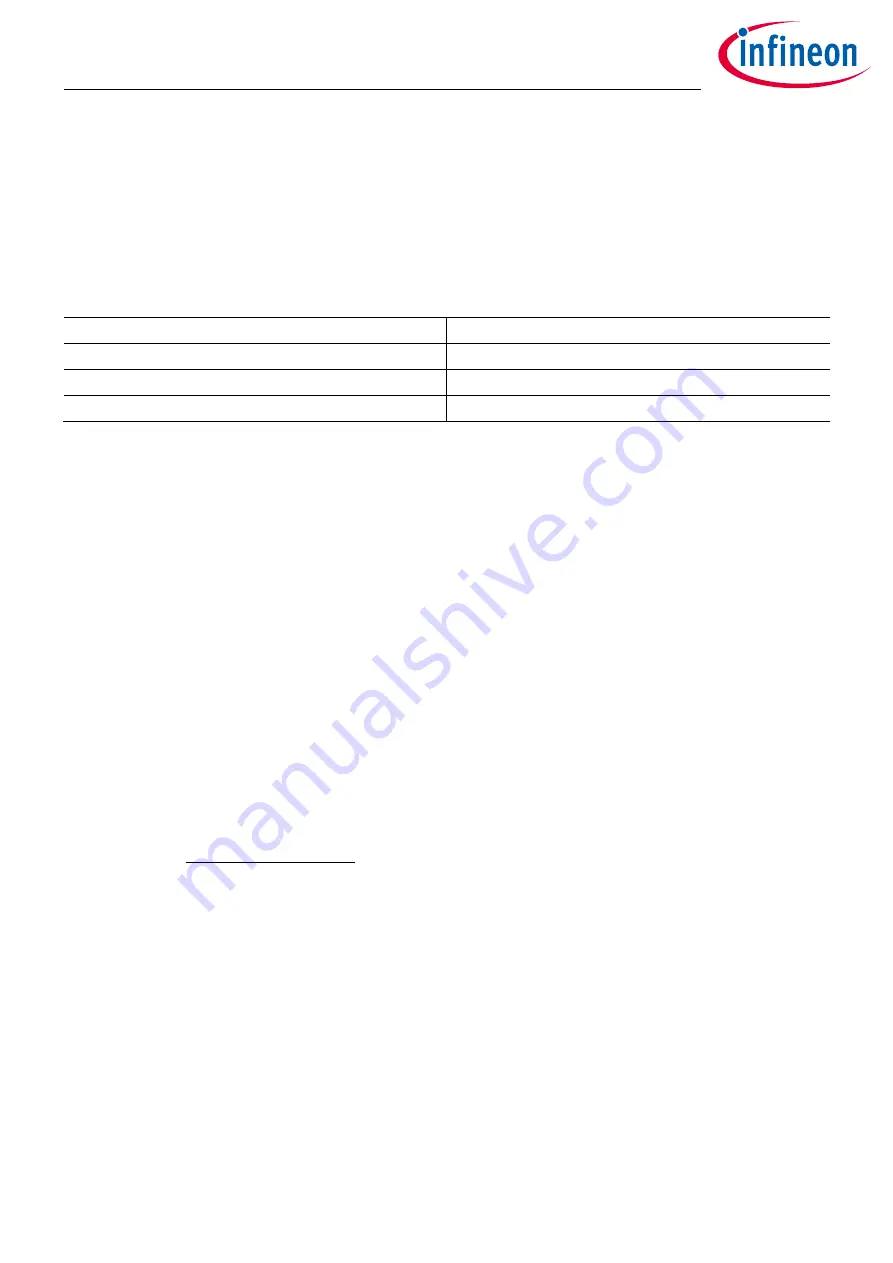

Modulation type settings

rampX_m_flavor

Modulation type

0

Dual edge (DE)

1

Leading edge (LE)

2, 3

Trailing edge (TE)

7.1.2

PWM ramp synchronization

Both ramp generators, ramp0 and ramp1, are capable of synchronizing to an external sync signal. In addition,

ramp1 synchronizes to ramp0 even without the presence of an external sync signal. The synchronization is

programmed through the register

rampX_sync_sel

(X = 0, 1).

For ramp0 programming, the register

ramp0_sync_sel

should always be set to 1. Thus, ramp0 synchronizes to

an external sync pulse if provided. Otherwise, its period is defined by register

tswitch0

(PAGE0.FREQUENCY_SWITCH). For ramp1 programming, the regiser

ramp1_sync_sel

should be programmed

as follows:

•

Set to 1, in order to synchronize to ramp0. If ramp0 is synchronized to an external sync pulse, ramp1 also

synchronizes to this pulse. This setting should be chosen for a dual-loop system with F

switch1

= F

switch0

or a

single-loop system with an interleaved phase.

•

Set to 0, to use the period defined by register

t

switch1

(PAGE1.FREQUENCY_SWITCH). This setting should be

chosen for a dual-loop system with F

switch1

≠ F

switch0

or a single-loop system using only Loop 1 (not typical).

The ramp phase in relation to the external sync pulse, (or ramp1 to ramp0 for internal sync) is defined by the

register

rampX_phase

(X = 0, 1). This is illustrated in

. The value for

rampX_phase

is automatically

computed by the FW from the PMBus command PAGEX.INTERLEAVE as given in Equation (7.3).

𝑟𝑎𝑚𝑝𝑋_𝑝ℎ𝑎𝑠𝑒 =

256∗𝑃𝐴𝐺𝐸𝑋.𝐼𝑁𝑇𝐸𝑅𝐿𝐸𝐴𝑉𝐸[3:0]

𝑃𝐴𝐺𝐸𝑋.𝐼𝑁𝑇𝐸𝑅𝐿𝐸𝐴𝑉𝐸[7:4]

(7.3)