User Manual

180 of 562

V 1.0

2021-08-25

XDPP1100 technical reference manual

Digital power controller

Digital pulse width modulator

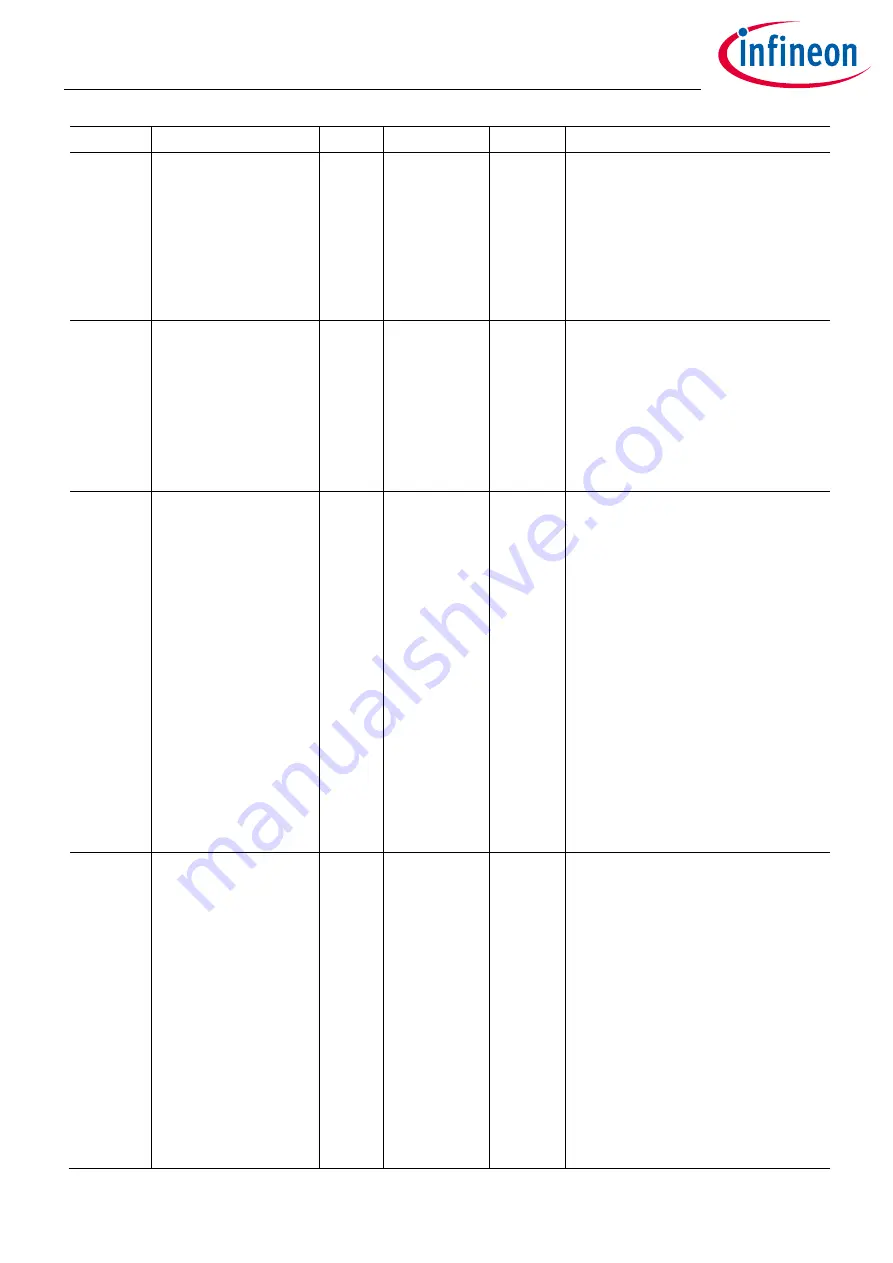

Peripheral Field name

Access Address

Bits

Description

0: Every T

switch

1: Every 2 T

switch

2: Every 4 T

switch

3: Every 8 T

switch

4: Every 16 T

switch

5: Every 32 T

switch

6: Every 64 T

switch

7: Every 64 T

switch

pwm

pwm_in_en_mask

RW

7000_2C90h [11:0]

When bit X is low, enables input

buffer on PWM[X+1] input pin. The

input buffer can then be used for

polling the state of the PWM output

via the common.io_inputs status

register. Setting low also asserts

interrupt PWM_IN_IRQ when the

enabled PWM inputs are high.

pid

pid_vrect_ref

RW

7000_1C00h

(pid0)

7000_2000h

(pid1)

[27:20]

Reference V

RECT

voltage for PID

coefficient scaling and variable

max. duty-cycle limit. PID

coefficients are scaled with V

RECT

to

maintain a constant loop gain. This

parameter defines the reference

V

RECT

voltage at which the gain scale

is 1.0. This parameter should be set

to the expected nominal V

RECT

voltage and it should be set before

optimization of PID coefficients K

P

,

K

I

and K

D

.

Example:

V

IN_nom

= 48 V, FB topology, N

turn

= 3

pid_vrect_ref = V

RECT_nom

= 48 V/3 =

16 V

LSB = 0.32 V, range = 0.0 to 81.6 V

pid

pid_verr_exit_thrs

RW

7000_1C0Ch

(pid0)

7000_200Ch

(pid1)

[6:0]

FTR mode error voltage (V

err

) exit

threshold where the error voltage is

defined as

V

err

= (target voltage - sense voltage)

When (V

err

is less than

pid_verr_exit_thrs) AND (V

err

slope <

pid_verr_slope_exit_thrs) the

control loop exits FTR mode.

Note:

This threshold is always positive,

indicating that the controller exits

FTR mode prior to the sensed

voltage overshooting the target.

LSB = 1.25 mV, range = 0.0 to

158.75 mV at VSEN