31.3.6 SPI match register high (SPIx_MH)

Refer to the description of the ML register.

Address: Base a 5h offset

Bit

7

6

5

4

3

2

1

0

Read

Write

Reset

0

0

0

0

0

0

0

0

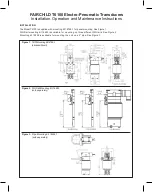

SPIx_MH field descriptions

Field

Description

Bits[15:8]

Hardware compare value (high byte)

31.3.7 SPI Data Register low (SPIx_DL)

This register, together with the DH register, is both the input and output register for SPI

data. A write to the registers writes to the transmit data buffer, allowing data to be queued

and transmitted.

When the SPI is configured as a master, data queued in the transmit data buffer is

transmitted immediately after the previous transmission has completed.

The SPTEF bit in the S register indicates when the transmit data buffer is ready to accept

new data. When the transmit DMA request is disabled (TXDMAE is 0): The S register

must be read when S[SPTEF] is set before writing to the SPI data registers; otherwise, the

write is ignored. When the transmit DMA request is enabled (TXDMAE is 1) when

S[SPTEF] is set, the SPI data registers can be written automatically by DMA without

reading the S register first.

Data may be read from the SPI data registers any time after S[SPRF] is set and before

another transfer is finished. Failure to read the data out of the receive data buffer before a

new transfer ends causes a receive overrun condition, and the data from the new transfer

is lost. The new data is lost because the receive buffer still held the previous character

and was not ready to accept the new data. There is no indication for a receive overrun

condition, so the application system designer must ensure that previous data has been

read from the receive buffer before a new transfer is initiated.

In 8-bit mode, only the DL register is available. Reads of the DH register return all zeros.

Writes to the DH register are ignored.

Memory map/register definition

MKW01Z128 MCU Reference Manual, Rev. 3, 04/2016

592

Freescale Semiconductor, Inc.

Summary of Contents for MKW01Z128

Page 7: ...MKW01xxRM Reference Manual Rev 3 04 2016 viii Freescale Semiconductor Inc...

Page 11: ...MKW01xxRM Reference Manual Rev 3 04 2016 xii Freescale Semiconductor Inc...

Page 133: ...MKW01Z128 MCU Reference Manual Rev 3 04 2016 2 Freescale Semiconductor Inc...

Page 233: ...Module clocks MKW01Z128 MCU Reference Manual Rev 3 04 2016 102 Freescale Semiconductor Inc...

Page 513: ...Interrupts MKW01Z128 MCU Reference Manual Rev 3 04 2016 382 Freescale Semiconductor Inc...

Page 633: ...CMP Trigger Mode MKW01Z128 MCU Reference Manual Rev 3 04 2016 502 Freescale Semiconductor Inc...