884

Chapter 28

On-Chip Debug Unit

Preliminary User’s Manual U17566EE1V2UM00

28.3 N-Wire Enabling Methods

28.3.1

Starting normal operation after RESET and RESPOC

For “normal operation” it has to be assured that the pins P05, P52…P55 are

available as port pins after either reset event. Therefore the software has to

perform OCDM.OCDM0 = 0 to make the pins available as port pins after

RESET.

Note that after any external reset via the RESET pin OCDM.OCDM0 is set to

"1" and the pins P05, P52…P55 are not available as application function pins

until the software sets OCDM.OCDM0 = 0.

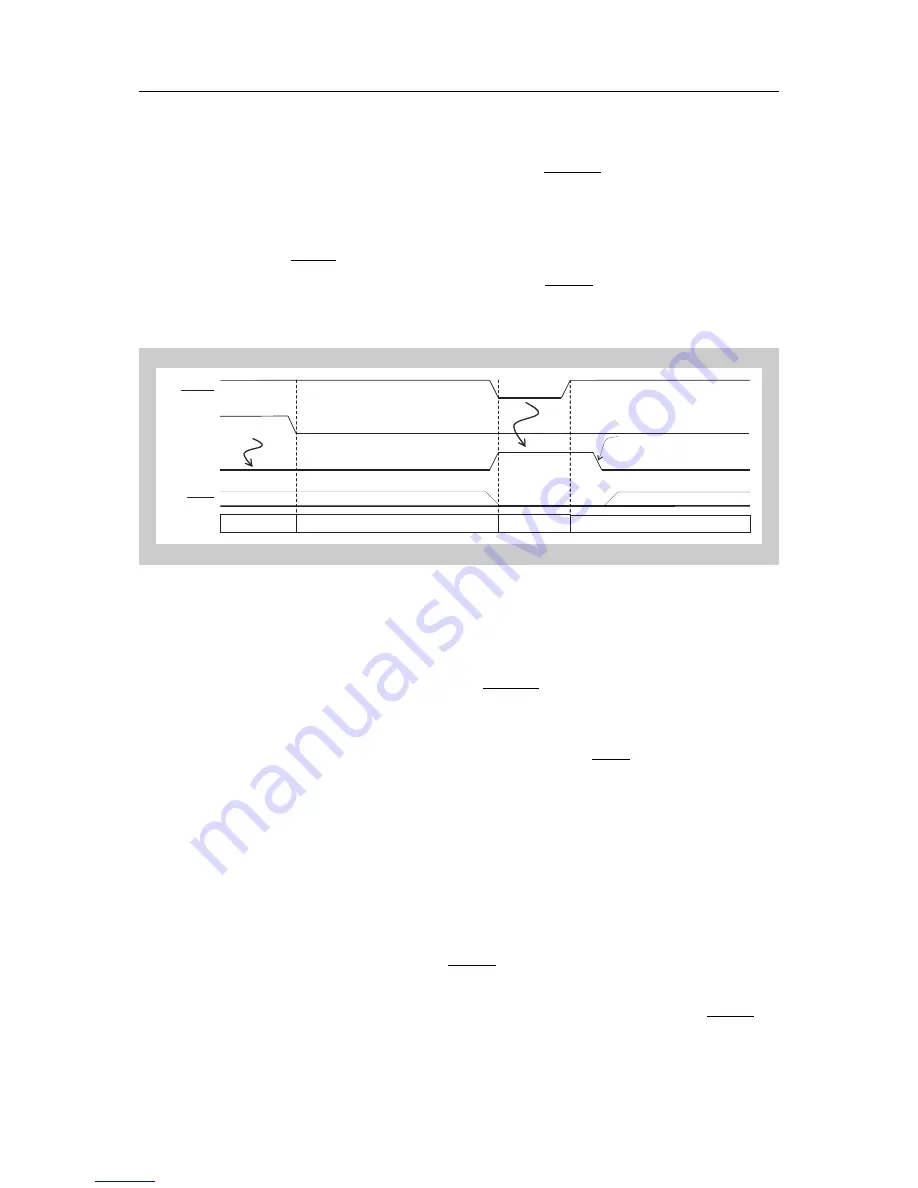

Figure 28-1

Start without N-Wire activation

28.3.2

Starting debugger after RESET and RESPOC

The software has to set OCDM.OCDM0 = 1 for enabling the N-Wire interface

also upon a RESPOC event. Afterwards the debugger may start to establish

communication with the controller by setting the DRST pin to high level and to

take control over the CPU.

On start of the debugger the entire controller is reset, i.e. all registers are set to

their default states and the CPU's program counter is set to the reset vector

0000 0000

H

with ROM mask devices respectively to the variable reset vector

for flash memory devices.

Note

After RESPOC the controller is operating without debugger control. Thus all

CPU instructions until the software performs OCDM.OCDM0 = 1 can not be

debugged. To restart the user’s program from beginning under the debugger’s

control apply an external RESET after the debugger has started, as shown in

Figure 28-2

. This will cause the program to restart. However the status of the

controller might not be the same as immediately after RESPOC, since the

internal RAM may have already been initialized, when the external RESET is

applied.

RESET

XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXXXXXX

RESPOC

OCDM0

P05/DRST

reset

normal operation

reset

normal operation

“0”

“1”

Application software

sets OCDM.OCDM0=0

electronic components distributor