TC1796

Peripheral Units (Vol. 2 of 2)

Controller Area Network (MultiCAN) Controller

User’s Manual

22-199

V2.0, 2007-07

MultiCAN, V2.0

22.9

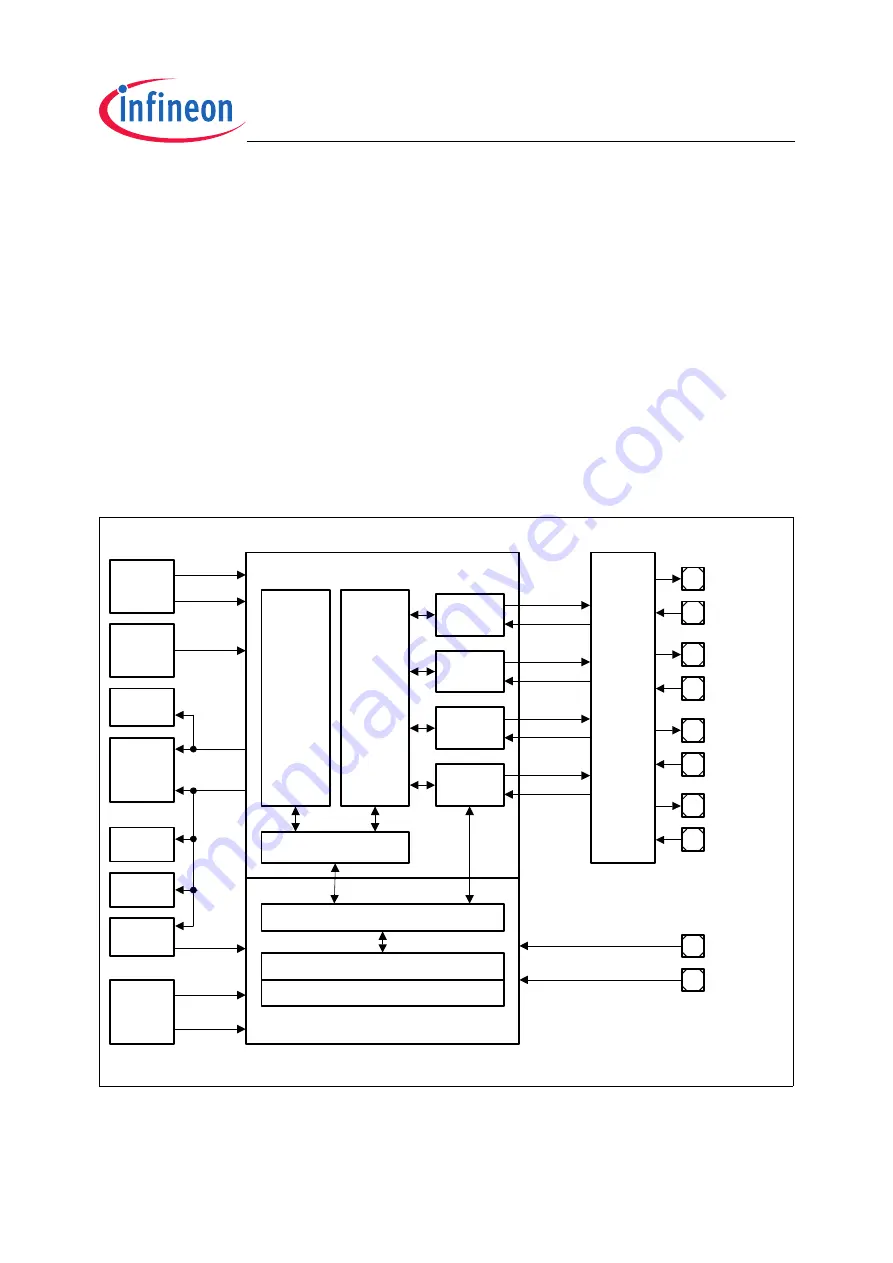

MultiCAN Module Implementation

This section describes CAN module interfaces with the clock control, port connections,

interrupt control, and address decoding.

22.9.1

Interfaces of the MultiCAN Module

shows the TC1796 specific implementation details and interconnections of

the MultiCAN module. The eight I/O lines of the MultiCAN module (two I/O lines of each

CAN node) are connected to I/O lines of Port 6. The MultiCAN module is also supplied

by clock control, interrupt control, and address decoding logic. MultiCAN interrupts can

be directed to the DMA controller and the GPTA modules. External trigger events for the

TTCAN can be generated by the GPTA0, the External Request Unit located in the SCU,

or directly through to pins. CAN interrupts are able to trigger DMA transfers and GPTA

operations.

Figure 22-38 CAN Module Implementation and Interconnections

MultiCAN Module Kernel

MCA05864

Port 6

Control

CAN

Node 1

CAN Control

Message

Object

Buffer

128

Objects

Timing Control and Synchronization

Scheduler

ScheduleTiming DataMemory

Time-Triggered Extension TTCAN

CAN

Node 0

CAN

Node 2

TXDC3

RXDC3

Linked

List

Control

P6.13 /

TXDCAN2

P6.12 /

RXDCAN2

P6.11 /

TXDCAN1

P6.10 /

RXDCAN1

P6.9 /

TXDCAN0

P6.8 /

RXDCAN0

CAN

Node 3

TXDC2

RXDC2

TXDC1

RXDC1

TXDC0

RXDC0

P6.15 /

TXDCAN3

P6.14 /

RXDCAN3

Interrupt

Control

f

CAN

f

CLC

Clock

Control

Address

Decoder

ECTT3

GPTA0

INT_

O15

DMA

INT_O

[3:0]

INT_O

[15:4]

P1.3 /

REQ3

P7.5 /

REQ7

ECTT1

ECTT2

SCU

Ext.Req.

Unit

GPTA1

LTCA2

ECTT4

ECTT5

A2

A2

A2

A2

A2

A2

A2

A2

A1

A1