548

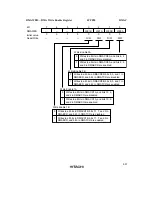

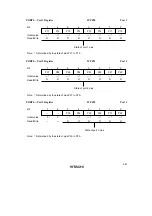

INTCR—Interrupt Control Register

H'FF31

Interrupt Controller

Bit

Initial value

Read/Write

7

—

0

—

6

—

0

—

5

INTM1

0

R/W

4

INTM0

0

R/W

3

NMIEG

0

R/W

2

—

0

—

1

—

0

—

0

—

0

—

NMI Edge Select

0

Interrupt request generated at falling edge

of NMI input

1

Interrupt request generated at rising edge

of NMI input

Interrupt Control Mode 1 and 0

0

1

0

1

Interrupts are controlled by I bit

Setting prohibited

Interrupts are controlled by bits I2 to I0, and IPR

Setting prohibited

INTM1

Description

0

—

2

—

Interrupt Control

Mode

0

1

INTM2

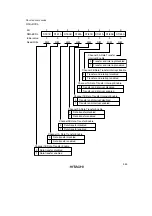

IER—IRQ Enable Register

H'FF32

Interrupt Controller

Bit

Initial value

Read/Write

15

IRQ15E

0

R/W

14

IRQ14E

0

R/W

13

IRQ13E

0

R/W

12

IRQ12E

0

R/W

11

IRQ11E

0

R/W

10

IRQ10E

0

R/W

9

IRQ9E

0

R/W

8

IRQ8E

0

R/W

Bit

Initial value

Read/Write

7

IRQ7E

0

R/W

6

IRQ6E

0

R/W

5

IRQ5E

0

R/W

4

IRQ4E

0

R/W

3

IRQ3E

0

R/W

2

IRQ2E

0

R/W

1

IRQ1E

0

R/W

0

IRQ0E

0

R/W

IRQ15 to IRQ0 Enable

0

IRQn interrupts disabled

1

IRQn interrupts enabled

(n = 15 to 0)

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...