607

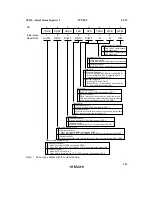

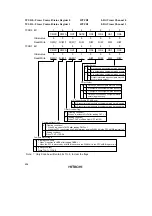

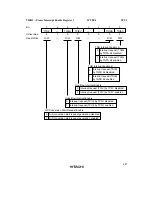

TCNT—Timer Counter

H'FFBC (W) H'FFBD (R)

WDT

Bit

Initial value

Read/Write

7

0

R/W

6

0

R/W

5

0

R/W

4

0

R/W

3

0

R/W

2

0

R/W

1

0

R/W

0

0

R/W

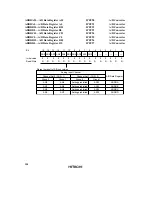

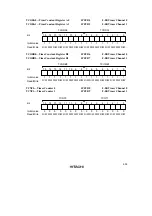

RSTCSR—Reset Control/Status Register

H'FFBE (W) H'FFBF (R)

WDT

Bit

Initial value

Read/Write

7

WOVF

0

R/(W)

*

6

RSTE

0

R/W

5

—

0

R/W

4

—

1

—

3

—

1

—

2

—

1

—

1

—

1

—

0

—

1

—

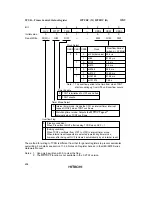

Reserved bit

Writes to this bit are invalid.

0 Internal reset is not performed when TCNT overflows

*

Internal reset is performed when TCNT overflows

Reset Enable

1

Note:

*

The chip is not initialized internally, but the TCNT and

TCSR registers in the WDT are reset.

0 [Clearing condition]

When 0 is written to WOVF after reading TCSR when WOVF = 1

[Setting condition]

When TCNT overflows (from H'FF to H'00) in watchdog timer mode

Watchdog Overflow Flag

1

Notes:

*

Can only be written with 0, to clear the flag.

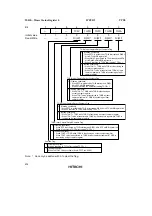

The method for writing to RSTCSR is different from that for general registers to prevent

accidental overwriting. For details see section 11.2.4, Notes on Register Access, in the

H8S/2678 Series Hardware Manual.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...