173

4.7.2

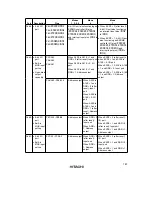

Pin States in Idle Cycle

Table 4.9 shows the pin states in an idle cycle.

Table 4.9

Pin States in Idle Cycle

Pins

Pin State

A23 to A0

Contents of following bus cycle

D15 to D0

High impedance

CSn

(n = 7 to 0)

High

*

1,

*

2

UCAS

,

LCAS

High

*

2

AS

High

RD

High

OE

High

HWR

,

LWR

High

DACKn

(n = 1, 0)

High

EDACKn

(n = 3 to 0)

High

Notes: 1. Remains low in DRAM space RAS down mode.

2. Remains low in a DRAM space refresh cycle.

4.8

Write Data Buffer Function

The H8S/2678 Series has a write data buffer function for the external data bus. Using the write

data buffer function enables external writes and DMA single address mode transfers to be

executed in parallel with internal accesses. The write data buffer function is made available by

setting the WDBE bit to 1 in the BCR register.

Figure 4.53 shows an example of the timing when the write data buffer function is used. When this

function is used, if an external write or DMA single address mode transfer continues for two states

or longer, and there is an internal access next, an external write only is executed in the first state,

but from the next state onward an internal access (on-chip memory or internal I/O register

read/write) is executed in parallel with the external write rather than waiting until it ends.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...