370

6.13

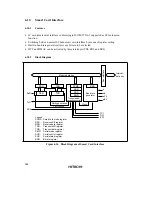

D/A Converter

6.13.1

Features

•

8-bit resolution

•

Output on two channels to maximum four channels

•

Maximum conversion time of 10 µs (with 20 pF capacitive load)

•

Output voltage of 0 V to Vref

•

D/A output hold function in software standby mode

•

Module stop mode can be set

6.13.2

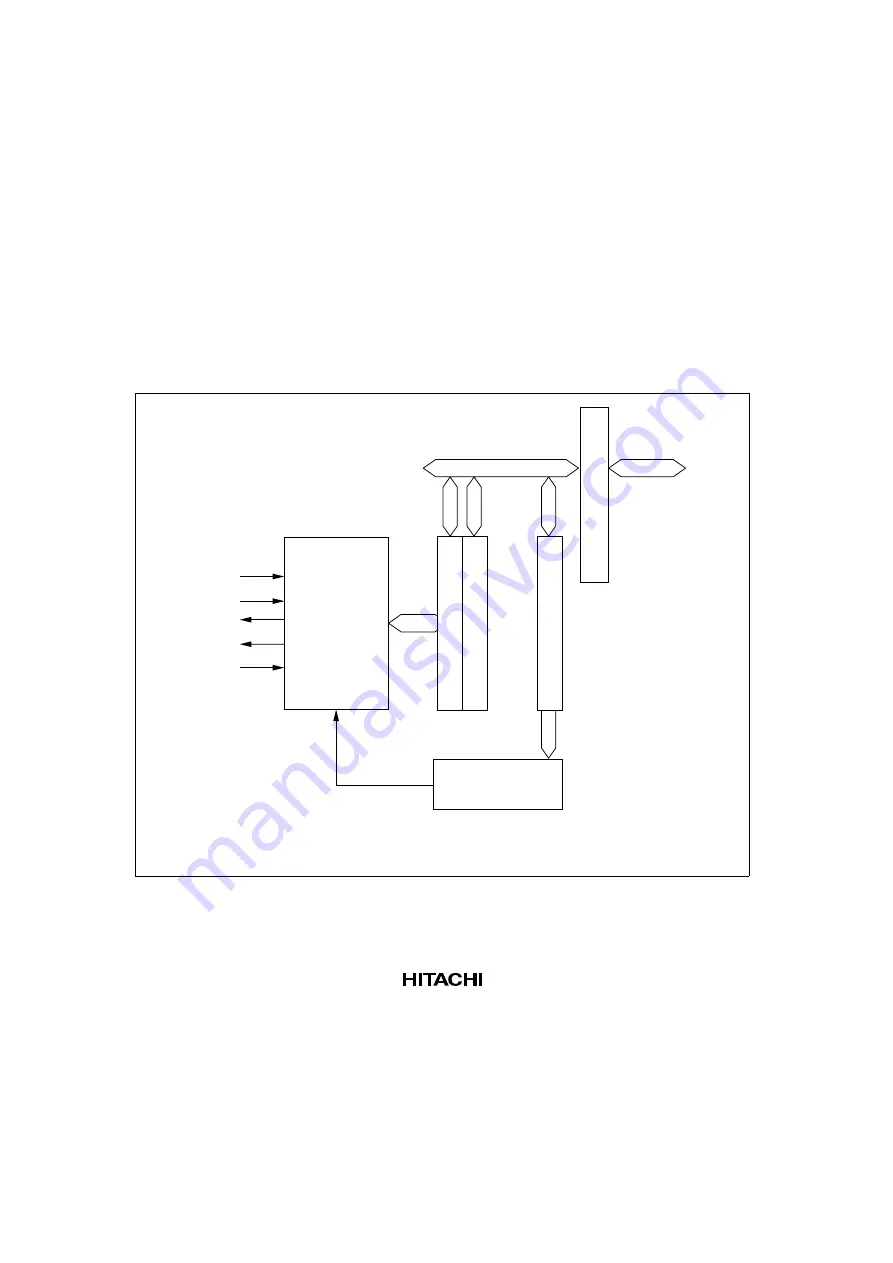

Block Diagram

Module data bus

Internal data bus

Vref

AVCC

DA1 (DA3)

DA0 (DA2)

AVSS

8-bit D/A

Control circuit

Bus interface

Legend

DACR01 (DACR23): D/A control register 01 (D/A control register 23)

DADR0 to DADR3:

D/A data registers 0 to 3

DADR0 (DADR2)

DADR1 (DADR3)

DACR01 (DACR23)

Figure 6.13 Block Diagram of D/A Converter

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...