248

•

Mode 4

When the corresponding bit of A23E to A16E is set to 1, setting a PADDR bit to 1 makes the

corresponding port A pin an address output, while clearing the bit to 0 makes the pin an input

port. Clearing one of bits A23E to A16 to 0 makes the corresponding port A pin an I/O port,

and its function can be switched with PADDR.

•

Mode 7 (when bit EXPE is set to 1 in SYSCR)

When the corresponding bit of A23E to A16E is set to 1, setting a PADDR bit to 1 makes the

corresponding port A pin an address output, while clearing the bit to 0 makes the pin an input

port. Clearing one of bits A23E to A16E to 0 makes the corresponding port A pin an I/O port;

setting the corresponding PADDR bit to 1 makes the pin an output port, while clearing the bit

to 0 makes the pin an input port.

•

Mode 7 (when bit EXPE is cleared to 0 in SYSCR)

Port A is an I/O port, and its pin functions can be switched with PADDR.

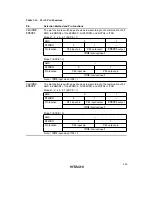

Port A Data Register (PADR)

Bit

7

6

5

4

3

2

1

0

PA7DR

PA6DR

PA5DR

PA4DR

PA3DR

PA2DR

PA1DR

PA0DR

Initial value

0

0

0

0

0

0

0

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

PADR is an 8-bit readable/writable register that stores output data for the port A pins (PA7 to

PA0).

PADR is initialized to H'00 by a reset and in hardware standby mode. It retains its prior state in

software standby mode.

Port A Register (PORTA)

Bit

7

6

5

4

3

2

1

0

PA7

PA6

PA5

PA4

PA3

PA2

PA1

PA0

Initial value

—

*

—

*

—

*

—

*

—

*

—

*

—

*

—

*

Read/Write

R

R

R

R

R

R

R

R

Note:

*

Determined by the state of pins PA7 to PA0.

PORTA is an 8-bit read-only register that shows the pin states. PORTA cannot be written to;

writing of output data for the port A pins (PA7 to PA0) must always be performed on PADR.

If a port A read is performed while PADDR bits are set to 1, the PADR values are read. If a port A

read is performed while PADDR bits are cleared to 0, the pin states are read.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...