595

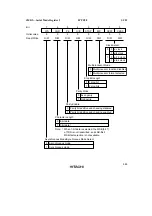

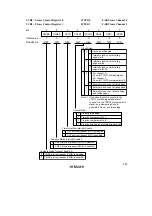

SSR2—Serial Status Register 2

H'FF8C

SCI2

Bit

Initial value

Read/Write

7

TDRE

1

R/(W)

*

6

RDRF

0

R/(W)

*

5

ORER

0

R/(W)

*

4

FER

0

R/(W)

*

3

PER

0

R/(W)

*

2

TEND

1

R

1

MPB

0

R

0

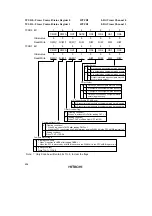

MPBT

0

R/W

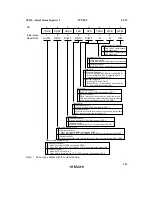

0 Data with a 0 multiprocessor

bit is transmitted

Data with a 1 multiprocessor

bit is transmitted

Multiprocessor Bit Transfer

1

0 [Clearing condition]

When data with a 0 multiprocessor bit is received

[Setting condition]

When data with a 1 multiprocessor bit is received

Multiprocessor Bit

1

0 [Clearing conditions]

• When 0 is written to TDRE after reading TDRE = 1

• When the DMAC or DTC is activated by a TXI

interrupt and writes data to TDR

[Setting conditions]

• When the TE bit in SCR is 0

• When TDRE = 1 at transmission of the last bit of

a 1-byte serial transmit character

Transmit End

1

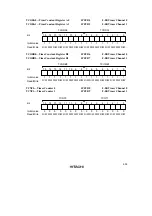

0 [Clearing condition]

When 0 is written to PER after reading PER = 1

[Setting condition]

When, in reception, the number of 1 bits in the receive

data plus the parity bit does not match the parity setting

(even or odd) specified by the O/

E

bit in SMR

Parity Error

1

0 [Clearing condition]

When 0 is written to FER after reading FER = 1

[Setting condition]

When the SCI checks the stop bit at the end of the receive data

when reception ends, and the stop bit is 0

Framing Error

1

0 [Clearing condition]

When 0 is written to ORER after reading ORER = 1

[Setting condition]

When the next serial reception is completed while RDRF = 1

Overrun Error

1

0 [Clearing conditions]

• When 0 is written to RDRF after reading RDRF = 1

• When the DMAC or DTC is activated by an RXI interrupt and reads data from RDR

[Setting condition]

When serial reception ends normally and receive data is transferred from RSR to RDR

Receive Data Register Full

1

0 [Clearing conditions]

• When 0 is written to TDRE after reading TDRE = 1

• When the DMAC or DTC is activated by a TXI interrupt and writes data to TDR

[Setting conditions]

• When the TE bit in SCR is 0

• When data is transferred from TDR to TSR and data can be written to TDR

Transmit Data Register Empty

1

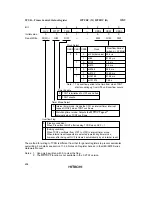

Note:

*

Can only be written with 0, to clear the flag.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...