145

4.5.9

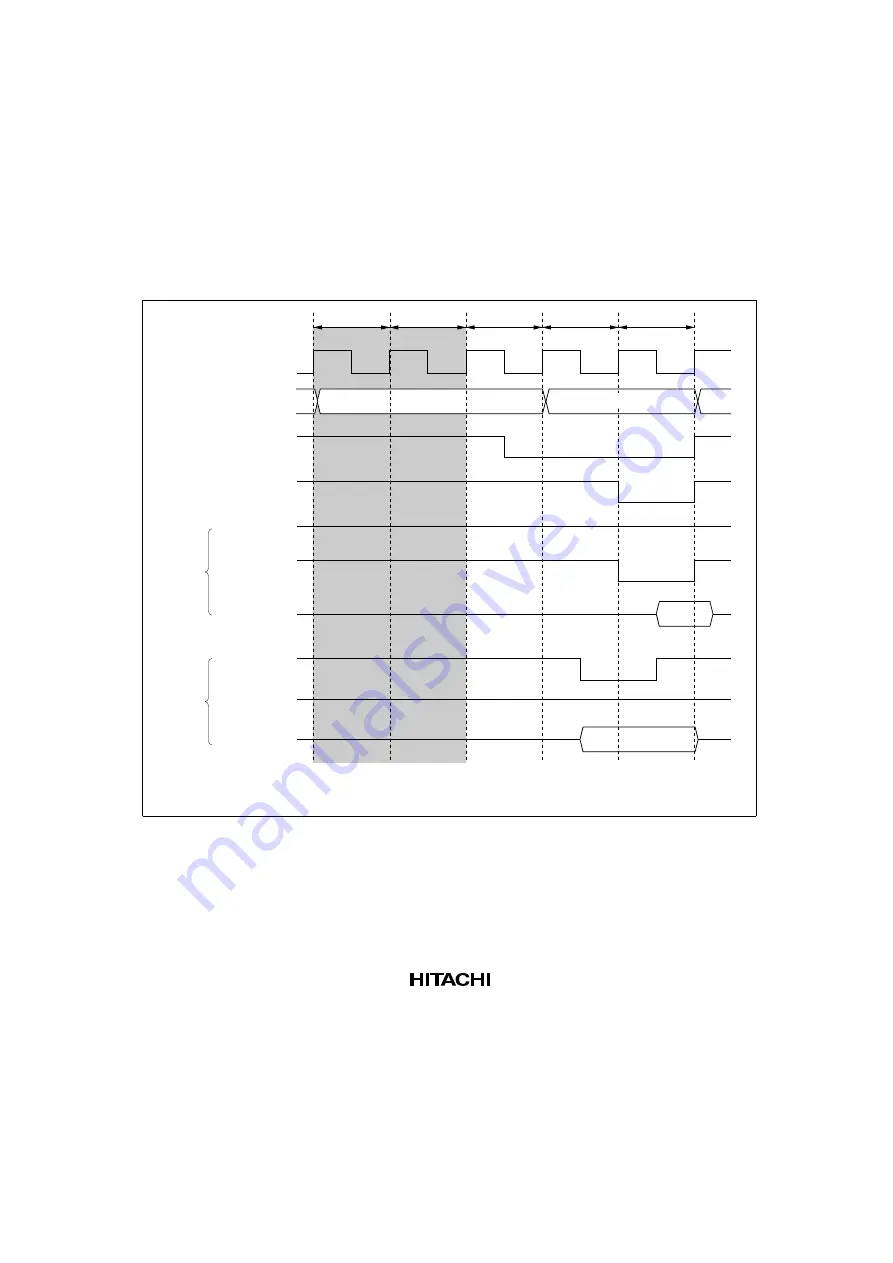

Precharge State Control

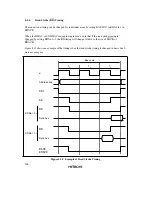

When DRAM is accessed, a

RAS

precharge time must be secured. With the H8S/2678 Series, one

T

p

state is always inserted when DRAM space is accessed. From one to four T

p

states can be

selected by setting bits TPC1 and TPC0 in DRACCR. Set the optimum number of T

p

cycles

according to the DRAM connected and the operating frequency of the chip. Figure 4.24 shows the

timing when two Tp states are inserted.

The setting of bits TPC1 and TPC0 is also valid for T

p

states in refresh cycles.

T

p1

ø

RASn

(

CSn

)

Read

Write

UCAS

,

LCAS

WE

(

HWR

)

OE

(

RD

)

Data bus

WE

(

HWR

)

OE

(

RD

)

Data bus

Address bus

T

p2

T

r

T

c1

T

c2

Row address

Column address

High

High

Note: n = 2 to 5

Figure 4.24 Example of Timing with Two-State Precharge Cycle

(RAST = 0, CAST = 0)

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...