111

Bit 4

EDDS

Description

0

Full access is always executed when EXDMAC single address transfer is performed

in DRAM space

(Initial value)

1

Burst access is possible when EXDMAC single address transfer is performed in

DRAM space

Bit 3—Reserved: This is a readable/writable bit, but the write value should always be 0.

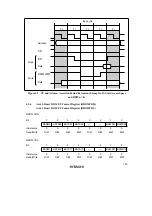

Bits 2 to 0—Address Multiplex Select (MXC2 to MXC0): These bits select the size of the shift

toward the lower half of the row address in row address/column address multiplexing. In burst

operation on the DRAM interface, these bits also select the row address bits to be used for

comparison.

Bit 2

MXC2

Bit 1

MXC1

Bit 0

MXC0

Description

0

0

0

8-bit shift

(Initial value)

•

When 8-bit access space is designated:

Row address bits A23 to A8 used for comparison

•

When 16-bit access space is designated:

Row address bits A23 to A9 used for comparison

1

9-bit shift

•

When 8-bit access space is designated:

Row address bits A23 to A9 used for comparison

•

When 16-bit access space is designated:

Row address bits A23 to A10 used for comparison

1

0

10-bit shift

•

When 8-bit access space is designated:

Row address bits A23 to A10 used for comparison

•

When 16-bit access space is designated:

Row address bits A23 to A11 used for comparison

1

11-bit shift

•

When 8-bit access space is designated:

Row address bits A23 to A11 used for comparison

•

When 16-bit access space is designated:

Row address bits A23 to A12 used for comparison

1

—

—

Reserved (setting prohibited)

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...