67

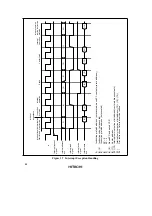

Figure 3.3 shows the timing of the setting of IRQnF.

ø

IRQn

input pin

IRQnF

Figure 3.3 Timing of Setting of IRQnF

The vector numbers for IRQ15 to IRQ0 interrupt exception handling are 31 to 16.

Detection of IRQ15 to IRQ0 interrupts does not depend on whether the relevant pin has been set

for input or output. When a pin is used as an external interrupt input pin, clear the corresponding

DDR bit to 0 and do not use the pin as an I/O pin for another function.

When interrupt request generation by a low level at the

IRQ

pin is selected for an IRQ15 to IRQ0

interrupt by means of an ISCR setting, when an interrupt is requested the relevant

IRQ

pin should

be held low until interrupt handling starts. The

IRQ

pin should then be returned to the high level,

and IRQnF (n = 0 to 15) cleared, in the interrupt handling routine. If the

IRQ

pin is returned to the

high level before interrupt handling is started, the associated interrupt may not be executed.

3.4.2

Internal Interrupts

There are 56 sources for internal interrupts from on-chip supporting modules.

1. For each on-chip supporting module there are flags that indicate the interrupt request status,

and enable bits that select enabling or disabling of these interrupts. If any one of these is set to

1, an interrupt request is issued to the interrupt controller.

2. The interrupt priority level can be set by means of IPR.

3. The DMAC and DTC can be activated by a TPU, SCI, or other interrupt request. When the

DMAC or DTC is activated by an interrupt, the interrupt control mode and CPU interrupt mask

bits have no effect.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...