406

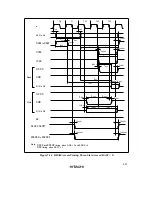

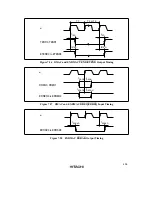

DMAC and EXDMAC Timing

Table 7.7

DMAC and EXDMAC Timing

Condition A*: V

CC

= 2.7 V to 3.6 V, AV

CC

= 2.7 V to 3.6 V, V

ref

= 2.7 V to AV

CC

,

V

SS

= AV

SS

= 0 V, ø = 2 MHz to 20 MHz, T

a

= –20°C to +75°C (regular

specifications), T

a

= –40°C to +85°C (wide-range specifications)

Condition B:

V

CC

= 3.0 V to 3.6 V, AV

CC

= 3.0 V to 3.6 V, V

ref

= 3.0 V to AV

CC

,

V

SS

= AV

SS

= 0 V, ø = 2 MHz to 33 MHz, T

a

= –20°C to +75°C (regular

specifications), T

a

= –40°C to +85°C (wide-range specifications)

* In planning stage

Condition A

Condition B

Test

Item

Symbol

Min

Max

Min

Max

Unit

Conditions

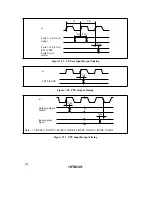

DREQ

setup time

t

DRQS

30

—

25

—

ns

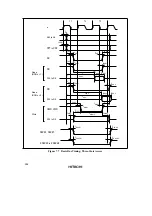

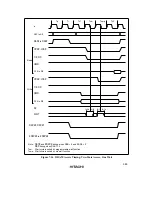

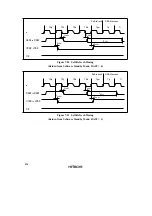

Figure7.27

DREQ

hold time

t

DRQH

10

—

10

—

TEND

delay time

t

TED

—

20

—

18

ns

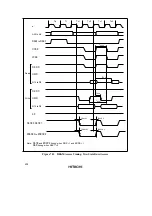

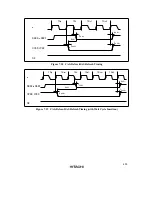

Figure7.26

DACK

delay time 1

t

DACD1

—

20

—

18

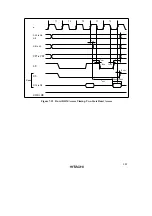

Figure7.24

DACK

delay time 2

t

DACD2

—

20

—

18

Figure7.25

EDREQ

setup time

t

EDRQS

30

—

25

—

ns

Figure7.27

EDREQ

hold time

t

EDRQH

10

—

10

—

ETEND

delay time

t

ETED

—

20

—

18

ns

Figure7.26

EDACK

delay time 1

t

EDACD1

—

20

—

18

Figure7.24

EDACK

delay time 2

t

EDACD2

—

20

—

18

Figure7.25

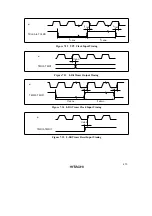

EDRAK

delay time

t

EDRKD

—

20

—

18

ns

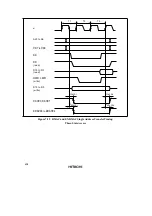

Figure7.28

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...