523

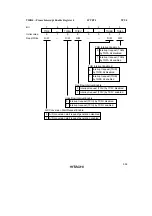

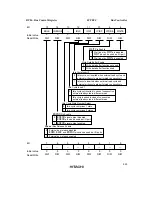

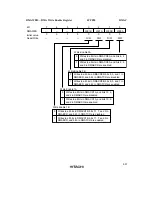

BCR—Bus Control Register

H'FECC

Bus Controller

Bit

Initial value

Read/Write

15

BRLE

0

R/W

14

BREQOE

0

R/W

13

—

0

R/W

12

IDLC

1

R/W

11

ICIS1

1

R/W

10

ICIS0

1

R/W

9

WDBE

0

R/W

8

WAITE

0

R/W

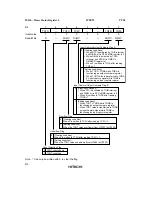

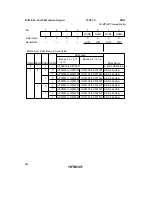

Bit

Initial value

Read/Write

7

—

0

R/W

6

—

0

R/W

5

—

0

R/W

4

—

0

R/W

3

—

0

R/W

2

—

0

R/W

1

—

0

R/W

0

—

0

R/W

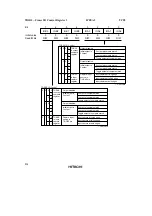

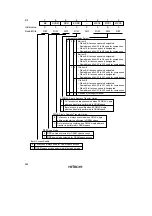

WAIT

Pin Enable

0

Wait input by

WAIT

pin disabled

WAIT

pin can be used as I/O port

1

Wait input by

WAIT

pin enabled

Write Data Buffer Enable

0

Write data buffer function not used

1

Write data buffer function used

Idle Cycle Insert 0

0

Idle cycle not inserted when external read cycle and

external write cycle are performed consecutively

1

Idle cycle inserted when external read cycle and

external write cycle are performed consecutively

Idle Cycle Insert 1

0

Idle cycle not inserted in case of consecutive

external read cycles in different areas

1

Idle cycle inserted in case of consecutive

external read cycles in different areas

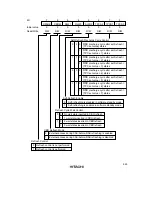

BREQO

Pin Enable

0

BREQO

signal output disabled

BREQO

pin can be used as I/O port

1

BREQO

signal output enabled

External Bus Release Enable

0

External bus release disabled

BREQ

,

BACK

, and

BREQO

pins can be used as I/O ports

1

External bus release enabled

Idle Cycle State Number Select

0

Idle cycle comprises 1 state

1

Idle cycle comprises 2 states

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...