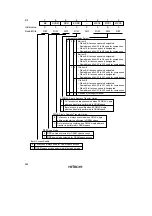

526

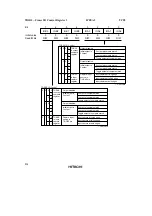

Bit

Initial value

Read/Write

7

BE

0

R/W

6

RCDM

0

R/W

5

DDS

0

R/W

4

EDDS

0

R/W

3

—

0

R/W

2

MXC2

0

R/W

1

MXC1

0

R/W

0

MXC0

0

R/W

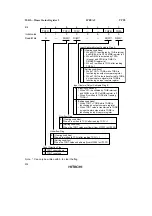

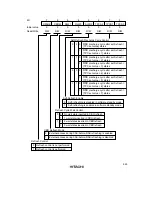

Address Multiplex Select

0

8-bit shift

• When 8-bit access space is designated:

Row address bits A23 to A8 used for comparison

• When 16-bit access space is designated:

Row address bits A23 to A9 used for comparison

0

1

9-bit shift

• When 8-bit access space is designated:

Row address bits A23 to A9 used for comparison

• When 16-bit access space is designated:

Row address bits A23 to A10 used for comparison

10-bit shift

• When 8-bit access space is designated:

Row address bits A23 to A10 used for comparison

• When 16-bit access space is designated:

Row address bits A23 to A11 used for comparison

11-bit shift

• When 8-bit access space is designated:

Row address bits A23 to A11 used for comparison

• When 16-bit access space is designated:

Row address bits A23 to A12 used for comparison

Reserved (setting prohibited)

0

1

0

1

—

1

—

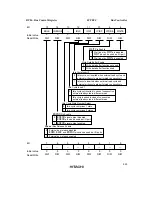

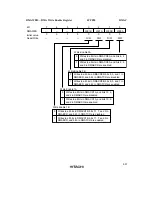

EXDMAC Single Address Transfer Option

0

Full access is always executed when EXDMAC single

address transfer is performed in DRAM space

1

Burst access is possible when EXDMAC single

address transfer is performed in DRAM space

DMAC Single Address Transfer Option

0

Full access is always executed when DMAC single

address transfer is performed in DRAM space

1

Burst access is possible when DMAC single address

transfer is performed in DRAM space

RAS

Down Mode

0

RAS

up mode selected for DRAM space access

1

RAS

down mode selected for DRAM space access

Burst Access Enable

0

Full access always used for DRAM space access

1

DRAM space access performed in fast page mode

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...