282

5.16

Port G

5.16.1

Overview

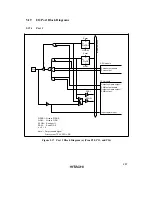

Port G is a 7-bit I/O port. Port G pins also function as bus control signal output pins (

BREQ

,

BACK

,

BREQO

, and

CS3

to

CS0

).

CS3

to

CS0

output can be enabled or disabled by making a

setting in PFCR0.

Figure 5.15 shows the port G pin configuration.

PG6 /

BREQ

PG5 /

BACK

PG4 /

BREQO

PG3 /

CS3

PG2 /

CS2

PG1 /

CS1

PG0 /

CS0

Port G

Port G pins

Pin functions in modes 1, 2, 4, 5, 6, and 7

PG6 (I/O) /

BREQ

(input)

PG5 (I/O) /

BACK

(output)

PG4 (I/O) /

BREQO

(output)

PG3 (I/O) /

CS3

(output)

PG2 (I/O) /

CS2

(output)

PG1 (I/O) /

CS1

(output)

PG0 (I/O) /

CS0

(output)

Figure 5.15 Port G Pin Functions

5.16.2

Register Configuration

Table 5.34 shows the port G register configuration.

Table 5.34

Port G Registers

Name

Abbreviation

R/W

Initial Value

Address

*

1

Port G data direction register

PGDDR

W

H'01/H'00

*

2

H'FE2F

Port G data register

PGDR

R/W

H'00

H'FF6F

Port G register

PORTG

R

Undefined

H'FF5F

Port function control register 0

PFCR0

R/W

H'FF

H'FE32

Notes: 1. Lower 16 bits of the address.

2. Initial value depends on the mode.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...