399

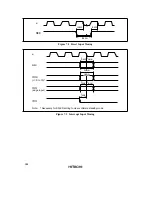

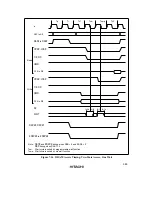

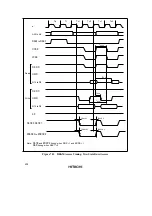

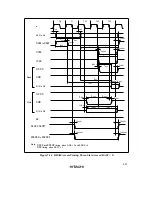

Tp

Tr

Tc1

Tcw

Tcwp

Tc2

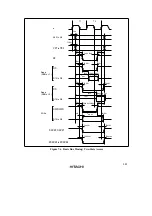

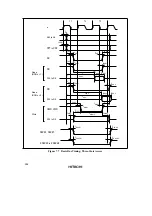

ø

A23 to A0

RAS5

to

RAS2

UCAS

,

LCAS

OE

,

RD

HWR

D15 to D0

UCAS

,

LCAS

OE

,

RD

HWR

t

WTS

t

WTH

t

WTS

t

WTH

D15 to D0

AS

WAIT

Read

Write

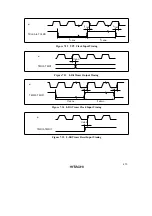

Tcw:

Wait cycle inserted by programmable wait function

Tcwp: Wait cycle inserted by pin wait function

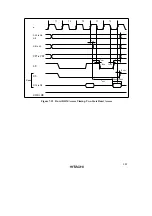

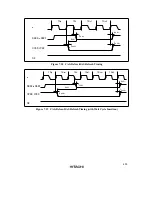

DACK0

,

DACK1

EDACK0

to

EDACK3

DACK

and

EDACK

timing: when DDS = 0 and EDDS = 0

RAS

timing: when RAST = 0

Note:

Figure 7.14 DRAM Access Timing: Two-State Access, One Wait

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...