93

4.1.2

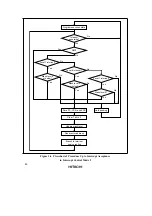

Block Diagram

Area decoder

Internal address bus

EXDMAC address bus

CS7

to

CS0

WAIT

BREQ

BACK

BREQO

External bus

control signals

Internal bus control signals

Internal data bus

Control registers

Address

selector

External bus

arbiter

External bus controller

Internal bus

arbiter

Internal bus controller

Internal bus master bus request signal

EXDMAC bus request signal

Internal bus master bus acknowledge signal

EXDMAC bus acknowledge signal

CPU bus request signal

DTC bus request signal

DMAC bus request signal

CPU bus acknowledge signal

DTC bus acknowledge signal

DMAC bus acknowledge signal

ABWCR

ASTCR

WTCRAH WTCRAL

WTCRBH WTCRBL

RDNCR

DRAMCRH DRAMCRL

DRACCR

REFCRH

REFCRL

RTCNT

RTCOR

CSACRH

CSACRL

BROMCRH BROMCRL

BCRL

BCRH

Figure 4.1 Block Diagram of Bus Controller

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...