345

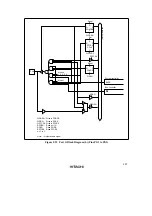

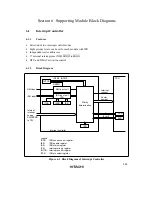

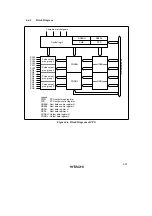

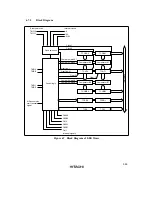

Section 6 Supporting Module Block Diagrams

6.1

Interrupt Controller

6.1.1

Features

•

Selection of two interrupt control modes

•

Eight priority levels can be set for each module with IPR

•

Independent vector addresses

•

17 external interrupt pins (NMI,

IRQ15

to

IRQ0

)

•

DTC and DMAC activation control

6.1.2

Block Diagram

INTCR

NMI input

IRQ input

Internal

interrupt

source

SWDTEND

to TEI

INTM1 INTM0

NMIEG

NMI input unit

IRQ input unit

ISR

ISCR

ITSR

IER

IPR

Interrupt controller

Priority

determination

Interrupt

request

Vector

number

I

I2 to I0

CCR

EXR

CPU

Legend

ISCR:

IRQ sense control register

IER:

IRQ enable register

ISR:

IRQ status register

IPR:

Interrupt priority register

INTCR: Interrupt control register

ITSR:

IRQ pin select register

Figure 6.1 Block Diagram of Interrupt Controller

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...