250

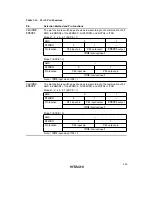

PFCR1 is an 8-bit readable/writable register that performs I/O port control. All the bits are valid in

modes 4 and 7, and bits 7 to 5 are valid in modes 1, 2, 5, and 6. PFCR1 is initialized to H'FF by a

reset and in hardware standby mode. It retains its prior state in software standby mode.

Bit 7—Address 23 Enable (A23E): Enables or disables output for address output 23 (A23).

Bit 7

A23E

Description

0

DR output when PA7DDR = 1

1

A23 output when PA7DDR = 1

(Initial value)

Bit 6—Address 22 Enable (A22E): Enables or disables output for address output 22 (A22).

Bit 6

A22E

Description

0

DR output when PA6DDR = 1

1

A22 output when PA6DDR = 1

(Initial value)

Bit 5—Address 21 Enable (A21E): Enables or disables output for address output 21 (A21).

Bit 5

A21E

Description

0

DR output when PA5DDR = 1

1

A21 output when PA5DDR = 1

(Initial value)

Bit 4—Address 20 Enable (A20E): Enables or disables output for address output 20 (A20). Valid

only in modes 4 and 7.

Bit 4

A20E

Description

0

DR output when PA4DDR = 1

1

A20 output when PA4DDR = 1

(Initial value)

Bit 3—Address 19 Enable (A19E): Enables or disables output for address output 19 (A19). Valid

only in modes 4 and 7.

Bit 3

A19E

Description

0

DR output when PA3DDR = 1

1

A19 output when PA3DDR = 1

(Initial value)

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...