164

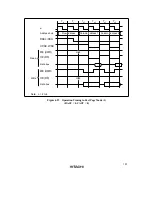

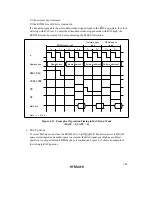

T1

Upper

address bus

Lower

address bus

ø

CSn

AS

Data bus

T2

T1

T1

Full access

RD

Burst access

Note: n = 1 or 0

Figure 4.43 Example of Burst ROM Access Timing (2)

(ASTn = 0, 1-State Burst Cycle)

4.6.3

Wait Control

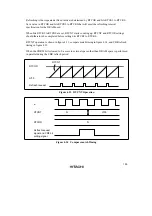

As with the basic bus interface, either (1) program wait insertion or (2) pin wait insertion using the

WAIT

pin can be used in the initial cycle (full access) on the burst ROM interface. See section

4.4.5, Wait Control.

Wait states cannot be inserted in a burst cycle.

4.6.4

Write Access

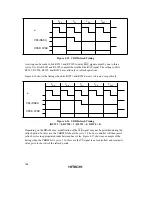

When a write access to burst ROM interface space is executed, burst access is interrupted at that

point and the write access is executed in line with the basic bus interface settings.

Write accesses are not performed in burst mode even though burst ROM space is designated.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...