550

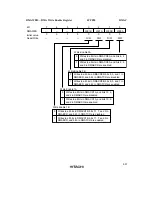

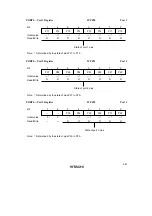

SBYCR—Standby Control Register

H'FF3A

System Control

Bit

Initial value

Read/Write

7

SSBY

0

R/W

6

OPE

1

R/W

5

—

0

—

4

—

0

—

3

STS3

1

R/W

2

STS2

1

R/W

1

STS1

1

R/W

0

STS0

1

R/W

Standby Timer Select 3 to 0

0

Reserved

1

0

1

Reserved

Reserved

Reserved

Reserved

Standby time = 64 states

Standby time = 512 states

Standby time = 1,024 states

Standby time = 2,048 states

Standby time = 4,096 states

Standby time = 16,384 states

Standby time = 32,768 states

Standby time = 65,536 states

Standby time = 131,072 states

Standby time = 262,144 states

Standby time = 524,288 states

0

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

1

0

1

0

0

1

1

0

1

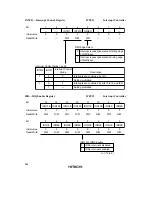

Output Port Enable

0

In software standby mode, address bus and bus control signals

are high-impedance

1

In software standby mode, address bus and bus control signals

retain output state

Software Standby

0

Transition to sleep mode after execution of SLEEP instruction

1

Transition to software standby mode after execution of SLEEP instruction

Note: In the F-ZTAT™ version, the flash memory

oscillation settling time must be secured.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...