528

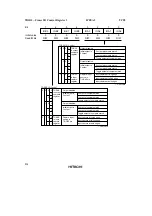

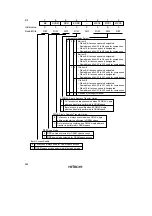

REFCR—Refresh Control Register

H'FED4

Bus Controller

Bit

Initial value

Read/Write

15

CMF

0

R/(W)

*

14

CMIE

0

R/W

13

RCW1

0

R/W

12

RCW0

0

R/W

11

—

0

R/W

10

RTCK2

0

R/W

9

RTCK1

0

R/W

8

RTCK0

0

R/W

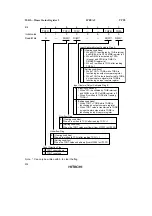

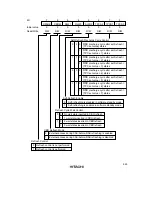

Refresh Counter Clock Select

0

Count operation halted

1

0

1

Count on ø/2

Count on ø/8

Count on ø/32

Count on ø/128

Count on ø/512

0

1

0

1

0

0

1

Count on ø/2048

1

0

Count on ø/4096

1

CAS

-

RAS

Wait Control

0

Wait state not inserted between

CAS

and

RAS

in refresh cycle

1

0

1

0

1

1 wait state inserted between

CAS

and

RAS

in refresh cycle

2 wait states inserted between

CAS

and

RAS

in refresh cycle

3 wait states inserted between

CAS

and

RAS

in refresh cycle

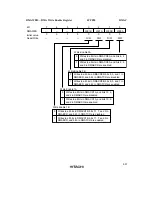

Compare Match Interrupt Enable

0

Interrupt request by CMF flag disabled

1

Interrupt request by CMF flag enabled

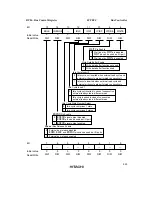

Compare Match Flag

0

[Clearing conditions]

• When 0 is written to CMF after reading CMF = 1 while the RFSHE

bit is cleared to 0

• When CBR refreshing is executed while the RFSHE bit is set to 1

1

[Setting condition]

When RTCOR = RTCNT

Note:

*

Only 0 can be written, to clear the flag.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...