104

BROMCRH and BROMCRL are 8-bit readable/writable registers used to make burst ROM

interface settings.

Area 1 and area 0 burst ROM interface settings can be made independently in BROMCRH and

BROMCRL, respectively.

BROMCRH and BROMCRL are initialized to H'0000 by a reset and in hardware standby mode.

They are not initialized in software standby mode.

Bit 7—Burst ROM Interface Select (BSRMn): Selects the burst ROM interface for area 0 or

area 1.

Bit 7

BSRMn

Description

0

Area n is basic bus interface space

(Initial value)

1

Area n is burst ROM interface space

(n = 1 or 0)

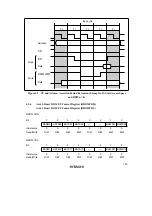

Bits 6 to 4—Burst Cycle Select (BSTSn2, BSTSn1, BSTSn0): These bits select the number of

burst cycle states.

Bit 6

BSTSn2

Bit 5

BSTSn1

Bit 4

BSTSn0

Description

0

0

0

Area n burst cycle comprises 1 state

(Initial value)

1

Area n burst cycle comprises 2 states

1

0

Area n burst cycle comprises 3 states

1

Area n burst cycle comprises 4 states

1

0

0

Area n burst cycle comprises 5 states

1

Area n burst cycle comprises 6 states

1

0

Area n burst cycle comprises 7 states

1

Area n burst cycle comprises 8 states

(n = 1 or 0)

Bits 3 and 2—Reserved: These are readable/writable bits, but the write value should always be 0.

Bits 1 and 0—Burst Word Length Select (BSWDn1, BSWDn0): These bits select the number

of words that can be burst-accessed on the burst ROM interface.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...