549

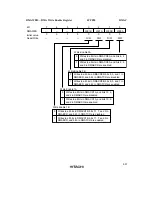

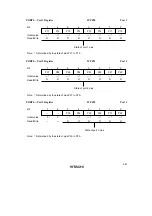

ISR—IRQ Status Register

H'FF34

Interrupt Controller

Bit

Initial value

Read/Write

15

IRQ15F

0

R/(W)

*

14

IRQ14F

0

R/(W)

*

13

IRQ13F

0

R/(W)

*

12

IRQ12F

0

R/(W)

*

11

IRQ11F

0

R/(W)

*

10

IRQ10F

0

R/(W)

*

9

IRQ9F

0

R/(W)

*

8

IRQ8F

0

R/(W)

*

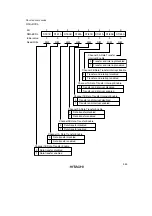

Bit

Initial value

Read/Write

7

IRQ7F

0

R/(W)

*

6

IRQ6F

0

R/(W)

*

5

IRQ5F

0

R/(W)

*

4

IRQ4F

0

R/(W)

*

3

IRQ3F

0

R/(W)

*

2

IRQ2F

0

R/(W)

*

1

IRQ1F

0

R/(W)

*

0

IRQ0F

0

R/(W)

*

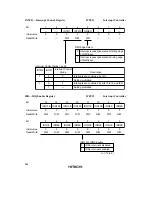

IRQ15 to IRQ0 Flags

0

[Clearing conditions]

• When 0 is written to IRQnF after reading IRQnF = 1

• When interrupt exception handling is executed when low-level detection

is set (IRQnSCB = IRQnSCA = 0) and

IRQn

input is high

• When IRQn interrupt exception handling is executed when falling, rising,

or both-edge detection is set (IRQnSCB = 1 or IRQnSCA = 1)

• When the DTC is activated by an IRQn interrupt and the DISEL bit in

MRB of the DTC is 0

1

[Setting conditions]

• When

IRQn

input goes low when low-level detection is set

(IRQnSCB = IRQnSCA = 0)

• When a falling edge occurs in

IRQn

input when falling edge detection is

set (IRQnSCB = 0, IRQnSCA = 1)

• When a rising edge occurs in

IRQn

input when rising edge detection is

set (IRQnSCB = 1, IRQnSCA = 0)

• When a falling or rising edge occurs in

IRQn

input when both-edge

detection is set (IRQnSCB = IRQnSCA = 1)

(n = 15 to 0)

Note:

*

Can only be written with 0, to clear the flag.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...