521

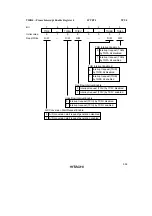

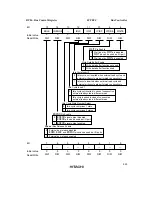

CSACRH, CSACRL—

CS

Assertion Period Control Registers H'FEC8

Bus Controller

Bit

Initial value

Read/Write

15

CSXH7

0

R/W

14

CSXH6

0

R/W

13

CSXH5

0

R/W

12

CSXH4

0

R/W

11

CSXH3

0

R/W

10

CSXH2

0

R/W

9

CSXH1

0

R/W

8

CSXH0

0

R/W

CS

and Address Signal Assertion Period Control 1

(n = 7 to 0)

0

In area n basic bus interface access, the

CSn

and

address assertion period (T

h

) is not extended

CSXHn

Description

1

In area n basic bus interface access, the

CSn

and

address assertion period (T

h

) is extended

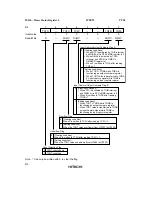

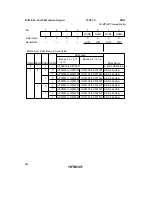

Bit

Initial value

Read/Write

CSACRH

CSACRL

7

CSXT7

0

R/W

6

CSXT6

0

R/W

5

CSXT5

0

R/W

4

CSXT4

0

R/W

3

CSXT3

0

R/W

2

CSXT2

0

R/W

1

CSXT1

0

R/W

0

CSXT0

0

R/W

CS

and Address Signal Assertion Period Control 2

(n = 7 to 0)

0

In area n basic bus interface access, the

CSn

and

address assertion period (T

t

) is not extended

CSXTn

Description

1

In area n basic bus interface access, the

CSn

and

address assertion period (T

t

) is extended

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...