484

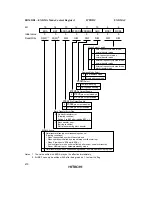

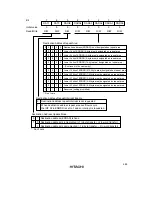

EDACR3—EXDMA Address Control Register 3

H'FDFE

EXDMAC

Bit

Initial value

Read/Write

15

SAT1

0

R/W

14

SAT0

0

R/W

13

SARIE

0

R/W

12

SARA4

0

R/W

11

SARA3

0

R/W

10

SARA2

0

R/W

9

SARA1

0

R/W

8

SARA0

0

R/W

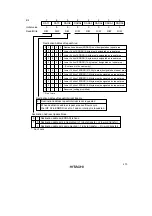

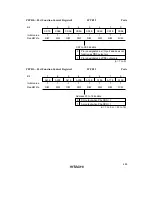

Source Address Repeat Interrupt Enable

0

Source address repeat interrupt is not requested

1

When source address repeat area overflow occurs, the IRF bit

in EDMDR is set to 1 and an interrupt is requested

Source Address Repeat Area

0

0

0

0

1

:

0

1

1

1

1

*

Source address (EDSAR) is not designated as repeat area

Lower 1 bit of EDSAR (2-byte area) designated as repeat area

Lower 2 bits of EDSAR (4-byte area) designated as repeat area

Lower 3 bits of EDSAR (8-byte area) designated as repeat area

Lower 4 bits of EDSAR (16-byte area) designated as repeat area

: (Continues in the same way)

Lower 19 bits of EDSAR (512-kbyte area) designated as repeat area

Lower 20 bits of EDSAR (1-Mbyte area) designated as repeat area

Lower 21 bits of EDSAR (2-Mbyte area) designated as repeat area

Lower 22 bits of EDSAR (4-Mbyte area) designated as repeat area

Lower 23 bits of EDSAR (8-Mbyte area) designated as repeat area

Reserved (setting prohibited)

*

: Don’t care

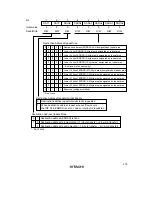

0

0

1

1

0

:

1

0

0

1

1

*

0

0

0

0

0

:

0

0

0

0

0

1

0

0

0

0

0

:

1

1

1

1

1

1

0

1

0

1

0

:

1

0

1

0

1

*

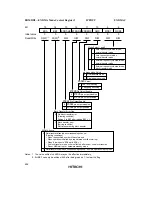

Source Address Update Mode

0

1

*

0

1

Source address (EDSAR) is fixed

Source address is incremented (+1 in byte transfer, +2 in word transfer)

Source address is decremented (–1 in byte transfer, –2 in word transfer)

*

: Don’t care

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...