537

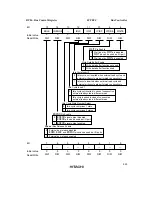

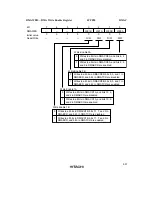

DMAWER—DMA Write Enable Register

H'FF20

DMAC

Bit

DMAWER

Initial value

Read/Write

7

—

0

—

6

—

0

—

5

—

0

—

4

—

0

—

3

WE1B

0

R/W

2

WE1A

0

R/W

1

WE0B

0

R/W

0

WE0A

0

R/W

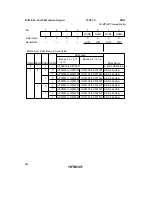

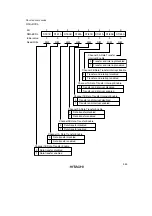

Write Enable 0A

0

Writes to all bits in DMACR0A, and bits 8, 4,

and 0 in DMABCR are disabled

1

Writes to all bits in DMACR0A, and bits 8, 4,

and 0 in DMABCR are enabled

Write Enable 0B

0

Writes to all bits in DMACR0B, bits 9, 5, and 1 in

DMABCR, and bit 4 in DMATCR are disabled

1

Writes to all bits in DMACR0B, bits 9, 5, and 1 in

DMABCR, and bit 4 in DMATCR are enabled

Write Enable 1A

0

Writes to all bits in DMACR1A, and bits 10, 6,

and 2 in DMABCR are disabled

1

Writes to all bits in DMACR1A, and bits 10, 6,

and 2 in DMABCR are enabled

Write Enable 1B

0

Writes to all bits in DMACR1B, bits 11, 7, and 3 in

DMABCR, and bit 5 in DMATCR are disabled

1

Writes to all bits in DMACR1B, bits 11, 7, and 3 in

DMABCR, and bit 5 in DMATCR are enabled

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...