606

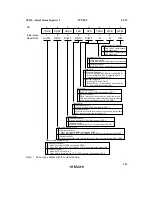

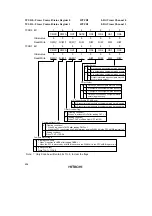

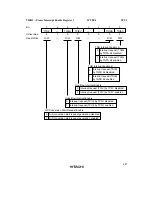

TCSR—Timer Control/Status Register

H'FFBC (W) H'FFBC (R)

WDT

Bit

Initial value

Read/Write

7

OVF

0

R/(W)

*

1

6

WT/

IT

0

R/W

5

TME

0

R/W

4

—

1

—

3

—

1

—

2

CKS2

0

R/W

1

CKS1

0

R/W

0

CKS0

0

R/W

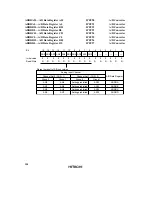

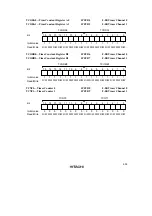

CKS2

Clock Select

0

1

Clock

ø/2 (Initial value)

ø/64

ø/128

ø/512

ø/2048

ø/8192

ø/32768

ø/131072

CKS1

0

1

0

1

CKS0

0

1

0

1

0

1

0

1

Overflow Period

*

(when ø = 20 MHz)

25.6

µ

s

819.2

µ

s

1.6 ms

6.6 ms

26.2 ms

104.9 ms

419.4 ms

1.68 s

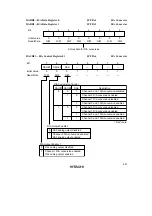

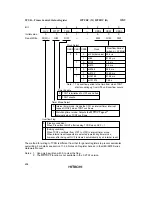

0 TCNT is initialized to H'00 and halted

TCNT counts

Timer Enable

1

Note:

*

The overflow period is the time from when TCNT

starts counting up from H'00 until overflow occurs.

0 Interval timer mode: Sends the CPU an interval timer interrupt

request (WOVI) when TCNT overflows

Watchdog timer mode: Outputs the

WDTOVF

signal

*

2

externally when TCNT overflows

Timer Mode Select

1

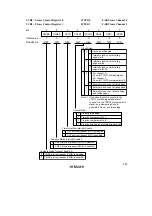

0 [Clearing condition]

When 0 is written to OVF after reading TCSR when OVF = 1

[Setting condition]

When TCNT overflows (from H'FF to H'00) in interval timer mode.

When internal reset requests are selected in watchdog timer mode,

however, after being set OVF is cleared automatically by an internal reset.

Overflow Flag

1

The method for writing to TCSR is different from that for general registers to prevent accidental

overwriting. For details see section 11.2.4, Notes on Register Access, in the H8S/2678 Series

Hardware Manual.

Notes: 1. Can only be written with 0, to clear the flag.

2. The

WDTOVF

function is not available in the F-ZTAT version.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...