391

ø

T1

T2

A23 to A0

CS7

to

CS0

AS

RD

D15 to D0

RD

D15 to D0

HWR

,

LWR

D15 to D0

Read

(RDNn = 1)

Read

(RDNn = 0)

Write

t

AD

t

CSD1

t

AS1

t

AS1

t

AS1

t

AS1

t

RSD1

t

RSD1

t

AC5

t

AA2

t

RSD1

t

WRD2

t

WSW1

t

WDH1

t

WDD

t

WRD2

t

AH1

t

AC2

t

RDS2

t

AA3

t

RSD2

t

RDS1

t

RDH1

t

AH1

t

ASD

t

ASD

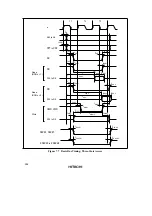

DACK0

,

DACK1

EDACK0

to

EDACK3

t

DACD1

t

DACD2

t

EDACD1

t

EDACD2

t

RDH2

Figure 7.6 Basic Bus Timing: Two-State Access

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...