155

Refreshing is thus repeated at fixed intervals determined by RTCOR and bits RTCK2 to RTCK0.

Set a value in RTCOR and bits RTCK2 to RTCK0 that will meet the refreshing interval

specification for the DRAM used.

When bits RTCK2 to RTCK0 are set, RTCNT starts counting up. RTCNT and RTCOR settings

should therefore be completed before setting bits RTCK2 to RTCK0.

RTCNT operation is shown in figure 4.33, compare match timing in figure 4.34, and CBR refresh

timing in figure 4.35.

When the CBRM bit is cleared to 0, access to external space other than DRAM space is performed

in parallel during the CBR refresh period.

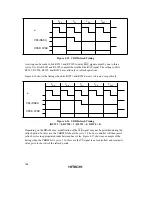

RTCOR

H'00

Refresh request

RTCNT

Figure 4.33 RTCNT Operation

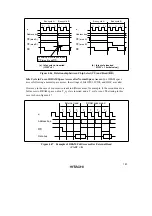

RTCNT

ø

N

RTCOR

N

H'00

Refresh request

signal and CMF bit

setting signal

Figure 4.34 Compare match Timing

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...