542

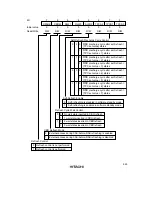

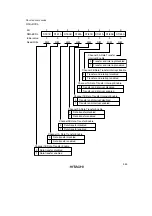

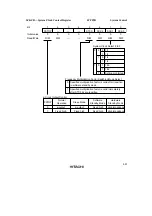

DMABCRH—DMA Band Control Register

H'FF26

DMAC

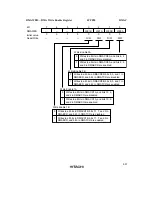

DMABCRL—DMA Band Control Register

H'FF27

DMAC

Full address mode

DMABCRH

Bit

DMABCRH

Initial value

Read/Write

15

FAE1

0

R/W

14

FAE0

0

R/W

13

—

0

R/W

12

—

0

R/W

11

DTA1

0

R/W

10

—

0

R/W

9

DTA0

0

R/W

8

—

0

R/W

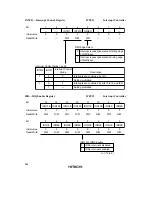

Channel 0 Data Transfer Acknowledge

0

Clearing of selected internal interrupt source

at time of DMA transfer is disabled

1

Clearing of selected internal interrupt source

at time of DMA transfer is enabled

Channel 1 Data Transfer Acknowledge

0

Clearing of selected internal interrupt source

at time of DMA transfer is disabled

1

Clearing of selected internal interrupt source

at time of DMA transfer is enabled

Channel 0 Full Address Enable

0

Short address mode

1

Full address mode

Channel 1 Full Address Enable

0

Short address mode

1

Full address mode

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...