354

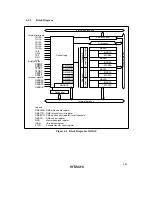

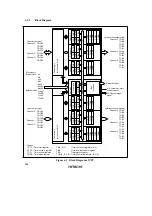

6.5.2

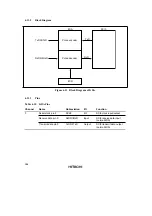

Block Diagram

Channel 3

TMDR

TIORL

TSR

TCR

TIORH

TIER

TGRA

TCNT

TGRB

TGRC

TGRD

Channel 4

TMDR

TSR

TCR

TIOR

TIER

TGRA

TCNT

TGRB

Channel 5

TMDR

TSR

TCR

TIOR

TIER

TGRA

TCNT

TGRB

Control logic

for channels 3 to 5

Channel 2

TMDR

TSR

TCR

TIOR

TIER

TGRA

TCNT

TGRB

TGRC

Channel 1

TMDR

TSR

TCR

TIOR

TIER

TGRA

TCNT

TGRB

Channel 0

TMDR

TSR

TCR

TIORH

TIER

Control logic

for channels 0 to 2

TGRA

TCNT

TGRB

TGRD

Bus

interface

Common

TSYR

Control logic

TSTR

[Input/output pins]

TIOCA3

TIOCB3

TIOCC3

TIOCD3

TIOCA4

TIOCB4

TIOCA5

TIOCB5

[Clock input]

ø/1

ø/4

ø/16

ø/64

ø/256

ø/1024

ø/4096

TCLKA

TCLKB

TCLKC

TCLKD

[Input/output pins]

TIOCA0

TIOCB0

TIOCC0

TIOCD0

TIOCA1

TIOCB1

TIOCA2

TIOCB2

[Interrupt request signals]

Channel 3:

Channel 4:

Channel 5:

[Interrupt request signals]

Channel 0:

Channel 1:

Channel 2:

Internal data bus

A/D conversion start

request signal

PPG output trigger

signal

TIORL

Module data bus

TGI3A

TGI3B

TGI3C

TGI3D

TCI3V

TGI4A

TGI4B

TCI4V

TCI4U

TGI5A

TGI5B

TCI5V

TCI5U

TGI0A

TGI0B

TGI0C

TGI0D

TCI0V

TGI1A

TGI1B

TCI1V

TCI1U

TGI2A

TGI2B

TCI2V

TCI2U

Channel 3:

Channel 4:

Channel 5:

Internal clock:

External clock:

Channel 0:

Channel 1:

Channel 2:

Legend

TSTR: Timer start register

TSYR: Timer synchro register

TCR:

Timer control register

TMDR: Timer mode register

TIOR (H, L):

Timer I/O control registers (H, L)

TIER:

Timer interrupt enable register

TSR:

Timer status register

TGR (A, B, C, D): Timer general registers (A, B, C, D)

Figure 6.5 Block Diagram of TPU

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...