483

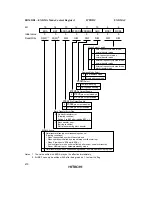

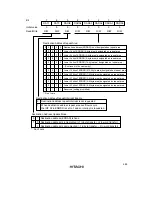

Bit

Initial value

Read/Write

7

EDIE

0

R/(W)

6

IRF

0

R/(W)

*

5

TCEIE

0

R/W

4

SDIR

0

R/W

3

DTSIZE

0

R/W

2

BGUP

0

R/W

1

—

0

R/W

0

—

0

R/W

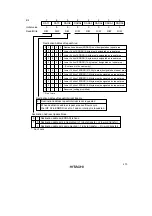

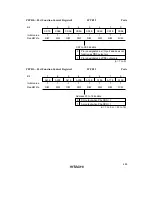

Bus Give-Up

0

Bus is not released in burst

mode or block transfer mode

1

In burst mode or block transfer

mode, the bus is transferred if

requested by an internal bus

master

Data Transmit Size

0

Byte-size (8-bit) specification

1

Word-size (16-bit) specification

Single Address Direction

0

Transfer direction: EDSAR

→

external device with DACK

1

Transfer direction: External device with DACK

→

EDDAR

Transfer Counter End Interrupt Enable

0

Transfer end interrupt requests by transfer counter are disabled

1

Transfer end interrupt requests by transfer counter are enabled

EXDMA Interrupt Enable

0

Interrupt request is not generated

1

Interrupt request is generated

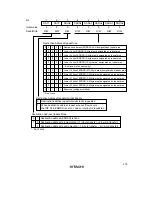

Interrupt Request Flag

0

No interrupt request source

[Clearing conditions]

• Writing 1 to the EDA bit in EDMDR

• Writing 0 to IRF after reading IRF = 1

1

Interrupt request source occurrence

[Setting conditions]

• Transfer end interrupt request generated by transfer counter

• Source address repeat area overflow interrupt request

• Destination address repeat area overflow interrupt request

Note:

*

Bit IRF can only be written with 0 after being read as 1, to clear the flag.

Summary of Contents for H8S/2670

Page 5: ......

Page 9: ......

Page 199: ...182 ...

Page 361: ...344 ...

Page 393: ...376 ...

Page 647: ...630 ...