Reset Control

89

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

System Control and Interrupts

1.3.2 Handling of Resets at System Level

This section explains resets at the subsystem level. It discusses how the master subsystem boot ROM

and the control subsystem boot ROM handles the reset causes after a reset.

1.3.2.1

Master Subsystem Reset Handling

The master subsystem, the Cortex-M3 CPU, and the Nested Vectored Interrupt Controller (NVIC) are all

reset by the Power-On Reset (POR) or the M3SYSRST reset signal. In both cases, the Cortex-M3 CPU

restarts program execution from the address provided by the reset entry in the vector table.

A register can later be referenced to determine the source of the reset. The M3SYSRST signal also

propagates to the Cortex-M3 peripherals and the rest of the Cortex-M3 subsystem. As shown in

, the M3SYSRST bit has four possible sources: XRS, M3WDOGS, M3SWRST, and M3DBGRST. The

M3WDOGS is set in response to time-out conditions of the two Cortex-M3 watchdogs or the Cortex-M3

NMI Watchdog. The M3SWRST is a software-generated reset output by the NVIC. The M3DBGRST is a

debugger-generated reset that is also output by the NVIC. In addition to driving M3SYSRST, these two

resets also propagate to the control subsystem and the analog subsystem. The M3RSnIN bit can be set in

the CRESCNF register to selectively reset the control subsystem from the master subsystem, and the

ACIBRST bit of the same register selectively resets the analog common interface bus. In addition to

driving reset signals to other parts of the chip, the master subsystem can also detect a C28SYSRST reset

being set in the control subsystem by reading the CRES bit of the CRESSTS register.

The master subsystem can also set bits in the SRCR register to selectively reset individual Cortex-M3

peripherals, provided they are enabled inside the respective device configuration (DC) register.

For all the reset causes shown in

, except for master software reset and master debugger reset,

both analog and control subsystems are also reset and held in reset. The master subsystem will be first

out of reset and starts executing software in master subsystem boot ROM. The master boot ROM brings

the control subsystem and analog subsystem out of reset. The control subsystem starts executing

software in the control subsystem boot ROM after it is out of reset. Refer to

and

for more details on how each boot ROM handles each reset cause.

provides summary of results of various reset operations on the master subsystem.

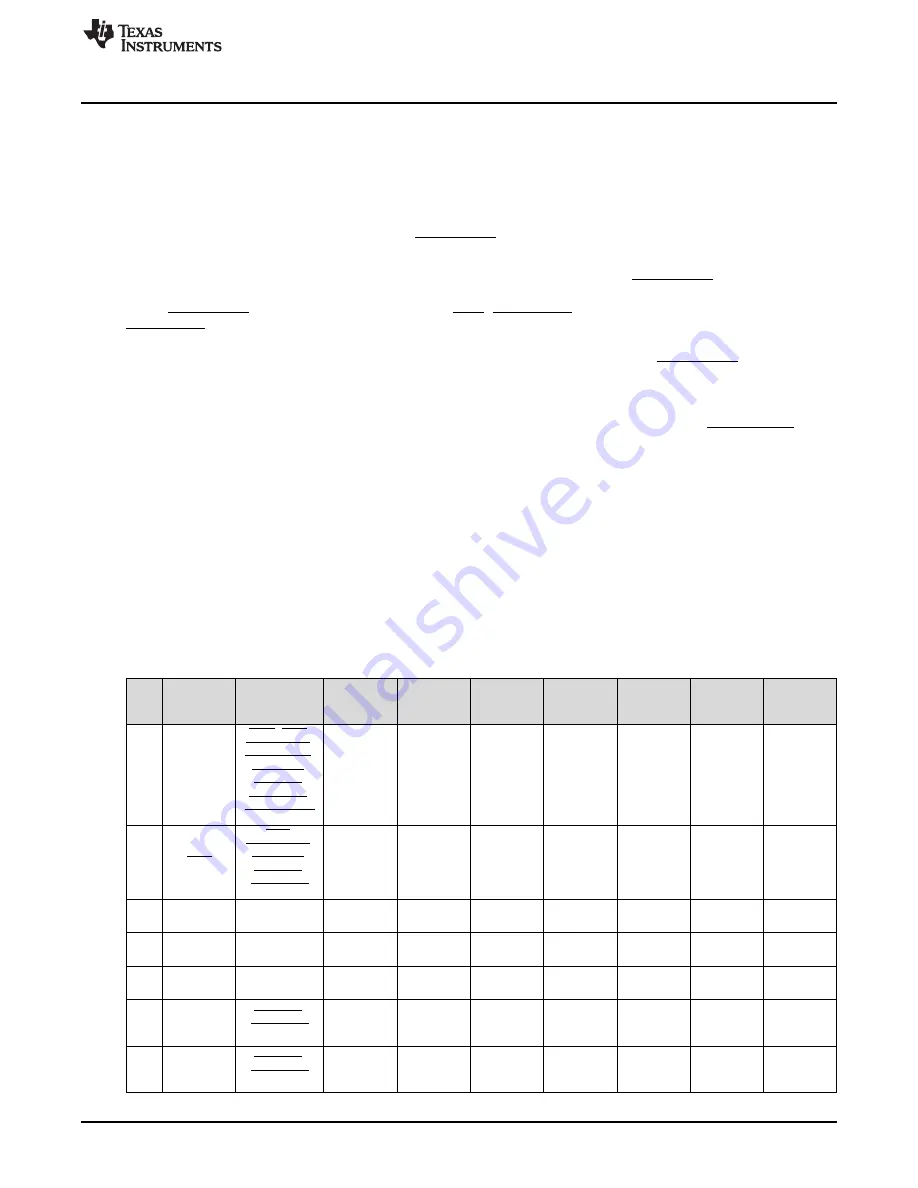

Table 1-5. Master Subsystem Rests, Signals and Effects

No.

Reset

Source

Device Reset

Signals

Asserted

Cortex-M3

CPU Core

Reset

JTAG

Reset

Master

Subsystem

Reset

Control

Subsystem

Reset

Analog

Subsystem

Reset

Shared

Resources

Reset

ACIB reset

1

POR

POR, XRS,

M3SYSRST,

M3PORRST,

ACIBRST,

SRXRST,

C28RSTIN,

C28SYSRTS

Yes

Yes

Yes

Yes

Yes

Yes

Yes

2

XRS

XRS,

M3SYSRST,

ACIBRST,

SRXRST,

C28RSTIN

Yes

Yes

Yes

Yes

Yes

Yes

Yes

3

WDT0 reset

Same as

above

Yes

Yes

Yes

Yes

Yes

Yes

Yes

4

WDT1 reset

Same as

above

Yes

Yes

Yes

Yes

Yes

Yes

Yes

5

MNMIWD

Same as

above

Yes

Yes

Yes

Yes

Yes

Yes

Yes

6

Master

Software

reset

SRXRST,

C28RSTIN

Yes

Yes

Yes

Yes

No

Yes

Yes

7

Master

Debugger

Reset

SRXRST,

C28RSTIN

Yes

Yes

Yes

Yes

No

Yes

Yes