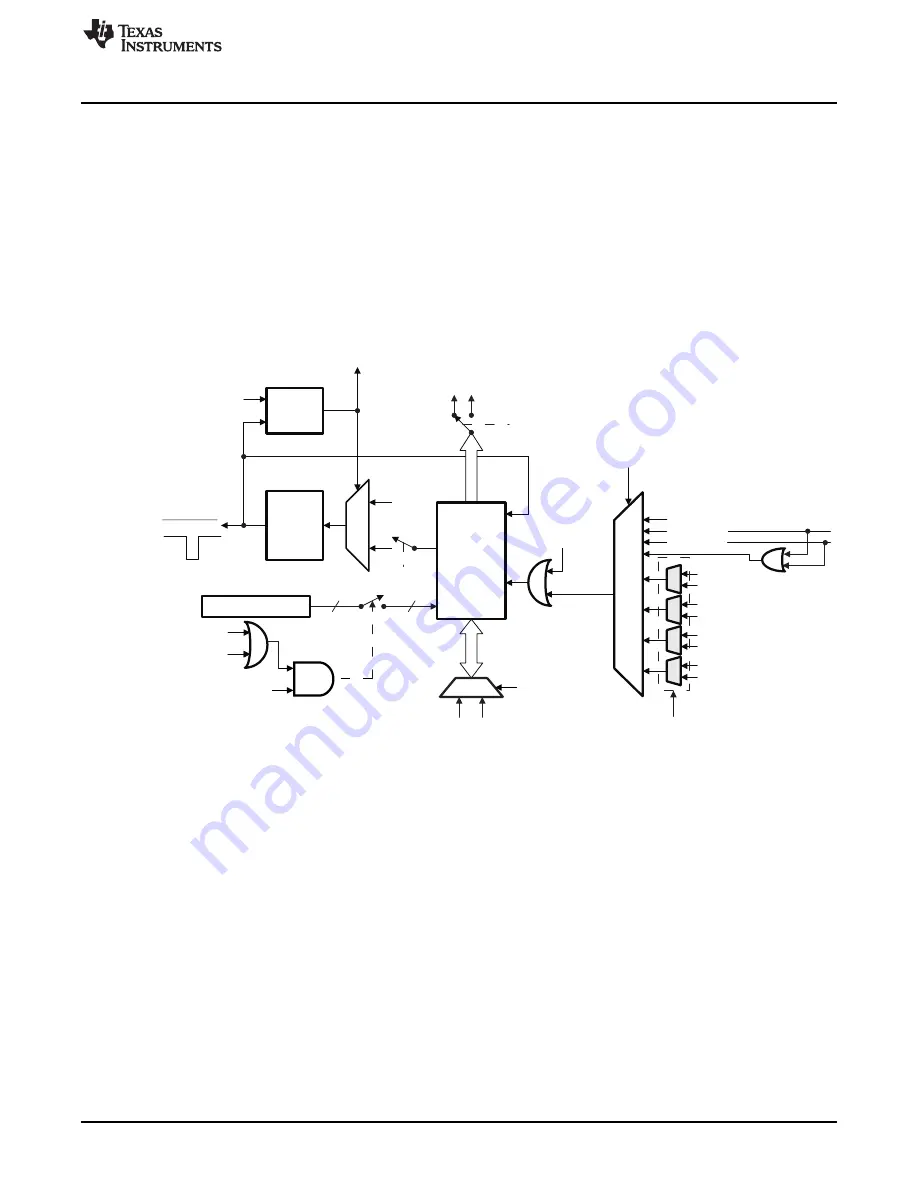

Latch

Generate

Interrupt

Pulse

When

Input = 1

4-bit

Counter

Set

Clear

1

0

0

Clear CNT

Inc CNT

ETPS[INTPRD]

ETCLR[INT]

EPWMxINT

ETFRC[INT]

ETSEL[INT]

000

001

010

011

100

0

ETFLG[INT]

CTR = Zero

CTR = PRD

ETSEL[INTSEL]

4

4

ETCNTINIT[INTINIT]

ETCNTINITCTL[INTINITFRC]

EPWMxSYNCI

ETCNTINITCTL[INTINITEN]

0

1

CTRU = CMPA

CTRU = CMPC

101

0

1

CTRD = CMPA

CTRD = CMPC

110

0

1

CTRU = CMPB

CTRU = CMPD

111

0

1

CTRD = CMPB

CTRD = CMPD

ETSEL[INTSELCMP]

0

1

ETINTPS[INTPRD2]

ETPS[INTPSSEL]

ETPS[INTCNT]

ETPS[INTPSSEL]

ETINTPS[INTCNT2]

0

1

ePWM Submodules

697

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Enhanced Pulse Width Modulator (ePWM) Module

Writing a 1 to the ETFRC[INT] bit will increment the event counter INTCNT. The counter will behave as

described above when INTCNT = INTPRD. When INTPRD = 0, the counter is disabled and hence no

events will be detected and the ETFRC[INT] bit is also ignored. The same applies to ETINTPS[INTCNT2]

& ETINTPS[INTPRD2]

The above definition means that you can generate an interrupt on every event, on every second event, or

on every third event if using the INTCNT and INTPRD. You can generate an interrupt on every event up to

15 events if using the INTCNT2 and INTPRD2.

The INTCNT2 value can be initialized with the value from ETCNTINIT[INTINIT] based on the selection

made in ETCNTINITCTL[INTINITEN]. When ETCNTINITCTL[INTINITEN] is set, then it enables

initialization of INTCNT2 counter with contents of ETCNTINIT[INTINIT] on a SYNC event or software force

determined by ETCNTINITCTL[INTINITFRC] .

Figure 7-44. Event-Trigger Interrupt Generator

shows the operation of the event-trigger's start-of-conversion-A (SOCA) pulse generator. The

enhancements include SOCASELCMP and SOCBSELCMP bit fields defined in the ETSEL register enable

CMPC and CMPD events respectively to cause a start of conversion. The ETPS[SOCPSSEL] bit field

determines whether SOCACNT2 and SOCAPRD2 take control or not. The ETPS[SOCACNT] counter and

ETPS[SOCAPRD] period values behave similarly to the interrupt generator except that the pulses are

continuously generated. That is, the pulse flag ETFLG[SOCA] is latched when a pulse is generated, but it

does not stop further pulse generation. The enable/disable bit ETSEL[SOCAEN] stops pulse generation,

but input events can still be counted until the period value is reached as with the interrupt generation logic.

The event that will trigger an SOCA and SOCB pulse can be configured separately in the

ETSEL[SOCASEL] and ETSEL[SOCBSEL] bits. The possible events are the same events that can be

specified for the interrupt generation logic with the addition of the DCAEVT1.soc and DCBEVT1.soc event

signals from the digital compare (DC) submodule. The SOCACNT2 initialization scheme is very similar to

the interrupt generator with respective enable, value initialize and SYNC or software force options.