1

7

n

7

n

1

1

1

1

1

1

1

1

S

Slave address

R/W ACK

Data

ACK

S

Slave address

R/W

ACK

Data

ACK

P

1

Any

number

1

Any number

I2C Module Operational Details

1015

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Inter-Integrated Circuit Module

14.2.5.3 Free Data Format

In this format (see

), the first byte after a START condition (S) is a data byte. An ACK bit is

inserted after each data byte, which can be from 1 to 8 bits, depending on the BC field of I2CMDR. No

address or data-direction bit is sent. Therefore, the transmitter and the receiver must both support the free

data format, and the direction of the data must be constant throughout the transfer.

To select the free data format, write 1 to the free data format (FDF) bit of I2CMDR. The free data format is

not supported in the digital loopback mode (DLB = 1 in I2CMDR).

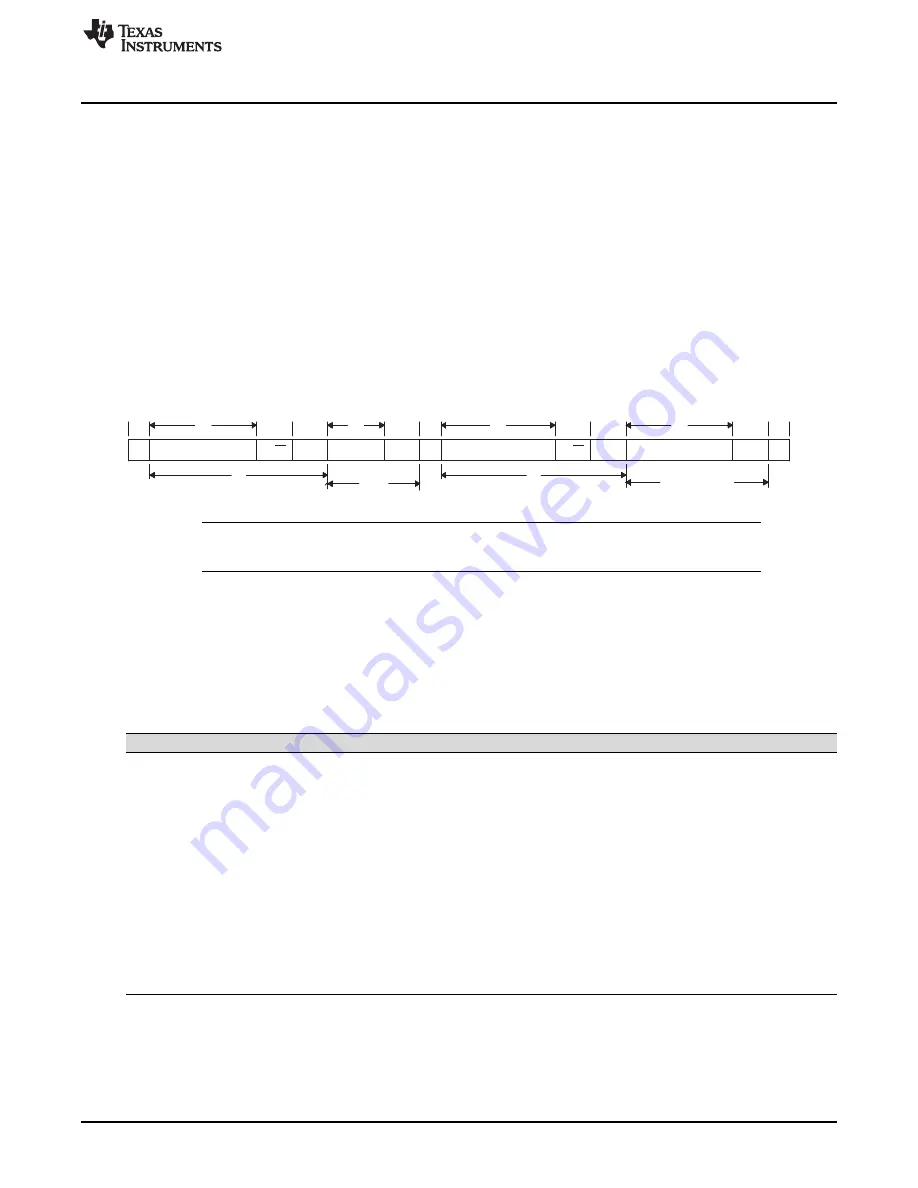

14.2.5.4 Using a Repeated START Condition

At the end of each data byte, the master can drive another START condition. Using this capability, a

master can communicate with multiple slave addresses without having to give up control of the bus by

driving a STOP condition. The length of a data byte can be from 1 to 8 bits and is selected with the BC

field of I2CMDR. The repeated START condition can be used with the 7-bit addressing, 10-bit addressing,

and free data formats.

shows a repeated START condition in the 7-bit addressing format.

Figure 14-10. Repeated START Condition (in This Case, 7-Bit Addressing Format)

NOTE:

In

, n = the number of data bits (from 1 to 8) specified by the bit count (BC) field

of I2CMDR.

14.2.6 NACK Bit Generation

When the I2C module is a receiver (master or slave), it can acknowledge or ignore bits sent by the

transmitter. To ignore any new bits, the I2C module must send a no-acknowledge (NACK) bit during the

acknowledge cycle on the bus.

summarizes the various ways you can tell the I2C module to

send a NACK bit.

Table 14-2. Ways to Generate a NACK Bit

I2C Module Condition

NACK Bit Generation Options

Slave-receiver modes

• Allow an overrun condition (RSFULL = 1 in I2CSTR)

• Reset the module (IRS = 0 in I2CMDR)

• Set the NACKMOD bit of I2CMDR before the rising edge of the last data bit you

intend to receive

Master-receiver mode AND

Repeat mode (RM = 1 in I2CMDR)

• Generate a STOP condition (STP = 1 in I2CMDR)

• Reset the module (IRS = 0 in I2CMDR)

• Set the NACKMOD bit of I2CMDR before the rising edge of the last data bit you

intend to receive

Master-receiver mode AND

Nonrepeat mode

(RM = 0 in I2CMDR)

• If STP = 1 in I2CMDR, allow the internal data counter to count down to 0 and thus

force a STOP condition

• If STP = 0, make STP = 1 to generate a STOP condition

• Reset the module (IRS = 0 in I2CMDR). = 1 to generate a STOP condition

• Set the NACKMOD bit of I2CMDR before the rising edge of the last data bit you

intend to receive