M3SSCLK

XCLKIN

DSDIVOVRIDE

DSOSCSRC

32KHZCLK

INTERNAL

OSC

OSCCLK

10MHZCLK

MAIN PLL

/2

X2

X1

M3 CPU

HCLK

FCLK

SLEEPDEEP

M3CLKENBx

EPI

I C (2)

2

SSI (4)

UART (5)

USB + PHY

(OTG)

EMAC

GP TIMER (4)

uCRC

WDOG 0

NMI WDOG

WDOG 1

CAN

1,2

USB PLL

GPIO_MUX1

/1

/2

…

/16

/1

/2

/4

uDMA

OSCCLK

SYSDIVSEL

M3SSCLK

M3DEEPSLEEP

ENABLE

CLOCK MODE

PERIPHERAL

CLOCK

ENABLES

RCC REG

RCGC REG

SCGS REG

M3RUN

M3SLEEP

M3DSDIVCLK

M3DEEPSLEEP

SYSCTRL REG

M3SSDIVSEL REG

M3SSDIVSEL

DCGC REG

DSLPCLKCFG REG

ACG

(Auto Clock Gate)

M3SSCLK

execution of WFI or WFE instr

activates low power modes

10MHZCLK

32KHZCLK

OSCCLK

DC REG

OSCCLK

XCLKIN

OSCCLK

OSCCLK

USBPLLCLK

MISSING

CLK DETECT

XCLKIN

INTR

NVIC

10MHZCLK

M3SSCLK

M3CLKENBx

CONTROL SUBSYSTEM

M3 NMI

CLOCKFAIL

MAIN OSC

10MHZCLK

CLOCKFAIL

OSCCLK

CLOCKFAIL

( GLOBAL PERIPHERAL ENABLES )

( CLOCK GATING – RUN )

( CLOCK GATING – SLEEP )

( CLOCK GATING – DEEP SLEEP )

M3SSCLK

REGISTER

ACCESS

REGISTER

ACCESS

PERIPH

LOGIC

M3SSCLK

SHARED

RESOURCES

IPC

PERIPH

LOGIC

CLOCKS

CLPMSTAT REG

SHARED

RAMS

MSG

RAMS

OFF

1

0

PLLSYSCLK

1

0

0

1

OSCCLK

ENTER A LOW POWER MODE

SELECTS TYPE

OF WAKEUP

SELECTS BETWEEN SLEEP

AND DEEP SLEEP MODES

ASSERT ANY INTERRUPT

TO EXIT SLEEP OR DEEP SLEEP

SYSPLLCTL REG

SYSPLLSTAT REG

SYSPLLMULT REG

SYSDIVSEL REG

MCLKREQUEST REG

M3SSCLK

/1

/2

/4

/8

SLEEPEXIT

Clock Control

128

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

System Control and Interrupts

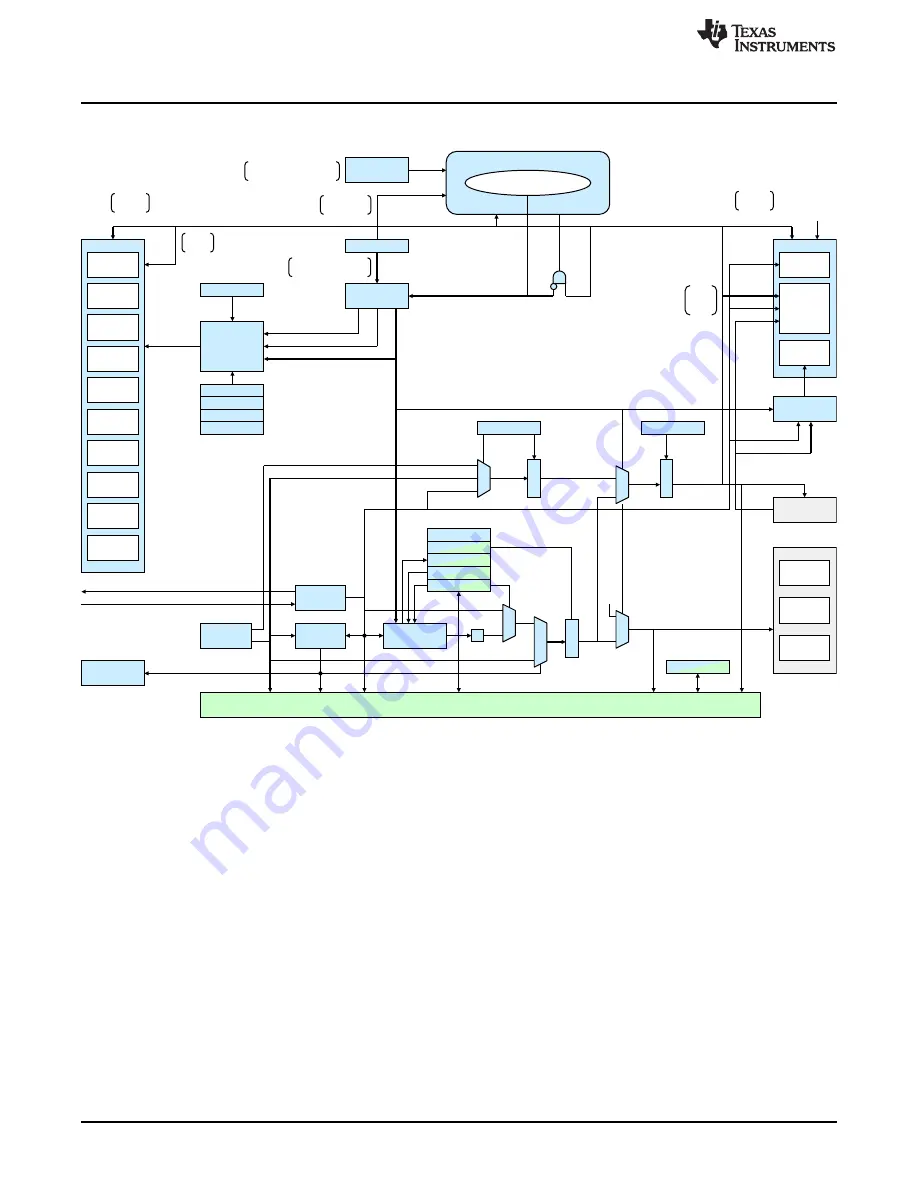

Figure 1-11. Master Subsystem Clocks and Low Power Mode Configuration

The internal PLLSYSCLK clock, normally used as a source for all clocks, is a divided-down output of the

Main PLL (referred to as the System PLL in some cases) or X1 external clock input, as defined by the

SPLLCKEN bit of the SYSPLLCTL register. There is also a second oscillator that internally generates two

clocks: 32KHZCLK and 10MHZCLK, as shown in the figure above.

The 32KHZCLK, 10MHZCLK, and OSCCLK clocks are used by the master subsystem as possible

sources for the deep sleep clock.

The Cortex-M3 master subsystem operates in one of three modes: run mode, sleep mode, or deep sleep

mode. Refer to

for more details on sleep mode and deep sleep mode of operation.

As shown in

, PLLSYSCLK is either derived from the output of the PLL (when the PLL is

enabled and locked) or from the MAIN OSC clock directly (when the PLL is bypassed or turned OFF)

divided by the SYSDIVSEL divider. This PLLSYSCLK is the input clock for the control subsystem and the

M3 system divider (M3SYSDIVSEL) whose output becomes M3SSCLK input to the master subsystem.

During Cortex-M3 normal mode of operation, the master subsystem is clocked by M3SSCLK and all the

master subsystem peripherals when enabled are clocked by M3SSCLK as configured in the RCGCx

registers. An exception is the Watchdog Timer 1 module which is clocked by OSCKCLK directly. The

USBPLL and CAN modules have the option to choose a clock source other than OSCCLK as shown in

. Refer to the respective sections for more details on USB and CAN clocking configurations.